Классификация, структура и основные характеристики современных микропроцессоров

Содержание:

Введение

Микропроцессор — процессор (устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде), реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем (в отличие от реализации процессора в виде электрической схемы на элементной базе общего назначения или в виде программной модели). Первые микропроцессоры появились в 1970-х годах и применялись в электронных калькуляторах, в них использовалась двоично-десятичная арифметика 4-битных слов. Вскоре их стали встраивать и в другие устройства, например, терминалы, принтеры и различную автоматику. Доступные 8-битные микропроцессоры с 16-битной адресацией позволили в середине 1970-х годов создать первые бытовые микрокомпьютеры.

Долгое время центральные процессоры создавались из отдельных микросхем малой и средней интеграции, содержащих от нескольких единиц до нескольких сотен транзисторов. Разместив целый процессор на одном чипе сверхбольшой интеграции, удалось значительно снизить его стоимость. Несмотря на скромное начало, непрерывное увеличение сложности микропроцессоров привело к почти полному устареванию других форм компьютеров. В настоящее время один или несколько микропроцессоров используются в качестве вычислительного элемента во всём, от мельчайших встраиваемых систем и мобильных устройств до огромных мейнфреймов и суперкомпьютеров.

В космических программах полётов к Луне «Аполлон» в 1960-х и 1970-х годах все бортовые вычисления для первичного наведения, навигации и управления были предоставлены небольшими специализированными процессорами бортового компьютера Аполлон.

С начала 1970-х годов широко известно, что рост мощности микропроцессоров следует закону Мура, который утверждает, что число транзисторов на интегральной микросхеме удваивается каждые 18 месяцев. В конце 1990-х главным препятствием для разработки новых микропроцессоров стало тепловыделение (TDP).

Некоторые авторы относят к микропроцессорам только устройства, реализованные строго на одной микросхеме. Такое определение расходится как с академическими источниками, так и с коммерческой практикой (например, варианты микропроцессоров Intel и AMD в корпусах типа SECC и подобных, такие, как Pentium II, были реализованы на нескольких микросхемах).

В настоящее время, в связи с очень незначительным распространением процессоров, не являющихся микропроцессорами, в бытовой лексике термины «микропроцессор» и «процессор» практически равнозначны.

Функции микропроцессора:

- вычисление адресов команд и операндов;

- выборка и дешифрация команд из основной памяти;

- выборка данных из основной памяти, регистров микропроцессорной памяти и регистров адаптеров внешних устройств;

- прием и обработка запросов и команд от адаптеров на обслуживание внешних устройств;

- обработка данных и их запись в основную память, регистры микропроцессорной памяти и регистры адаптеров внешних устройств;

- выработка управляющих сигналов для всех прочих узлов и блоков ПК;

- переход к следующей команде.

По числу больших интегральных схем (БИС) в микропроцессорном комплекте различают микропроцессоры однокристальные, многокристальные и многокристальные секционные.

Процессоры даже самых простых ЭВМ имеют сложную функциональную структуру, содержат большое количество электронных элементов и множество разветвленных связей. Изменять структуру процессора необходимо так, чтобы полная принципиальная схема или ее части имели количество элементов и связей, совместимое с возможностями БИС. При этом микропроцессоры приобретают внутреннюю магистральную архитектуру, т. е. в них к единой внутренней информационной магистрали подключаются все основные функциональные блоки (арифметико-логический, рабочих регистров, стека, прерываний, интерфейса, управления и синхронизации и др.).

Для обоснования классификации микропроцессоров по числу БИС надо распределить все аппаратные блоки процессора между основными тремя функциональными частями: операционной, управляющей и интерфейсной. Сложность операционной и управляющей частей процессора определяется их разрядностью, системой команд и требованиями к системе прерываний; сложность интерфейсной части разрядностью и возможностями подключения других устройств ЭВМ (памяти, внешних устройств, датчиков и исполнительных механизмов и др.). Интерфейс процессора содержит несколько десятков информационных шин данных (ШД), адресов (ША) и управления (ШУ).

Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы). По мере увеличения степени интеграции элементов в кристалле и числа выводов корпуса параметры однокристальных микропроцессоров улучшаются. Однако возможности однокристальных микропроцессоров ограничены аппаратными ресурсами кристалла и корпуса. Для получения многокристального микропроцессора необходимо провести разбиение его логической структуры на функционально законченные части и реализовать их в виде БИС (СБИС). Функциональная законченность БИС многокристального микропроцессора означает, что его части выполняют заранее определенные функции и могут работать автономно.

Операционный процессор служит для обработки данных, управляющий процессор выполняет функции выборки, декодирования и вычисления адресов операндов и также генерирует последовательности микрокоманд. Автономность работы и большое быстродействие БИС УП позволяет выбирать команды из памяти с большей скоростью, чем скорость их исполнения БИС ОП. При этом в УП образуется очередь еще не исполненных команд, а также заранее подготавливаются те данные, которые потребуются ОП в следующих циклах работы. Такая опережающая выборка команд экономит время ОП на ожидание операндов, необходимых для выполнения команд программ. Интерфейсный процессор позволяет подключить память и периферийные средства к микропроцессору; он, по существу, является сложным контроллером для устройств ввода/вывода информации. БИС ИП выполняет также функции канала прямого доступа к памяти.

Выбираемые из памяти команды распознаются и выполняются каждой частью микропроцессора автономно, и поэтому может быть обеспечен режим одновременной работы всех БИС МП, т. е. конвейерный поточный режим исполнения последовательности команд программы (выполнение последовательности с небольшим временным сдвигом). Такой режим работы значительно повышает производительность микропроцессора.

Многокристальные секционные микропроцессоры получаются в том случае, когда в виде БИС реализуются части (секции) логической структуры процессора при функциональном разбиении ее вертикальными плоскостями. Для построения многоразрядных микропроцессоров при параллельном включении секций БИС в них добавляются средства "стыковки".

Для создания высокопроизводительных многоразрядных микропроцессоров требуется столь много аппаратных средств, не реализуемых в доступных БИС, что может возникнуть необходимость еще и в функциональном разбиении структуры микропроцессора горизонтальными плоскостями. В результате рассмотренного функционального разделения структуры микропроцессора на функционально и конструктивно законченные части создаются условия реализации каждой из них в виде БИС. Все они образуют комплект секционных БИС МП.

Таким образом, микропроцессорная секция это БИС, предназначенная для обработки нескольких разрядов данных или выполнения определенных управляющих операций. Секционность БИС МП определяет возможность "наращивания" разрядности обрабатываемых данных или усложнения устройств управления микропроцессора при "параллельном" включении большего числа БИС.

Однокристальные и трехкристальные БИС МП, как правило, изготовляют на основе микроэлектронных технологий униполярных полупроводниковых приборов, а многокристальные секционные БИС МП на основе технологии биполярных полупроводниковых приборов. Использование многокристальных микропроцессорных высокоскоростных биполярных БИС, имеющих функциональную законченность при малой физической разрядности обрабатываемых данных и монтируемых в корпус с большим числом выводов, позволяет организовать разветвление связи в процессоре, а также осуществить конвейерные принципы обработки информации для повышения его производительности.

По назначению различают универсальные и специализированные микропроцессоры.

Универсальные микропроцессоры могут быть применены для решения широкого круга разнообразных задач. При этом их эффективная производительность слабо зависит от проблемной специфики решаемых задач. Специализация МП, т. е. его проблемная ориентация на ускоренное выполнение определенных функций позволяет резко увеличить эффективную производительность при решении только определенных задач.

Среди специализированных микропроцессоров можно выделить различные микроконтроллеры, ориентированные на выполнение сложных последовательностей логических операций, математические МП, предназначенные для повышения производительности при выполнении арифметических операций за счет, например, матричных методов их выполнения, МП для обработки данных в различных областях применений и т. д. С помощью специализированных МП можно эффективно решать новые сложные задачи параллельной обработки данных. Например, конволюция позволяет осуществить более сложную математическую обработку сигналов, чем широко используемые методы корреляции. Последние в основном сводятся к сравнению всего двух серий данных: входных, передаваемых формой сигнала, и фиксированных опорных и к определению их подобия. Конволюция дает возможность в реальном масштабе времени находить соответствие для сигналов изменяющейся формы путем сравнения их с различными эталонными сигналами, что, например, может позволить эффективно выделить полезный сигнал на фоне шума.

Разработанные однокристальные конвольверы используются в устройствах опознавания образов в тех случаях, когда возможности сбора данных превосходят способности системы обрабатывать эти данные.

По виду обрабатываемых входных сигналов различают цифровые и аналоговые микропроцессоры. Сами микропроцессоры – цифровые устройства, однако, могут иметь встроенные аналого-цифровые и цифро-аналоговые преобразователи. Поэтому входные аналоговые сигналы передаются в МП через преобразователь в цифровой форме, обрабатываются и после обратного преобразования в аналоговую форму поступают на выход. С архитектурной точки зрения такие микропроцессоры представляют собой аналоговые функциональные преобразователи сигналов и называются аналоговыми микропроцессорами. Они выполняют функции любой аналоговой схемы (например, производят генерацию колебаний, модуляцию, смещение, фильтрацию, кодирование и декодирование сигналов в реальном масштабе времени и т. д., заменяя сложные схемы, состоящие из операционных усилителей, катушек индуктивности, конденсаторов и т. д.). При этом применение аналогового микропроцессора значительно повышает точность обработки аналоговых сигналов и их воспроизводимость, а также расширяет функциональные возможности за счет программной "настройки" цифровой части микропроцессора на различные алгоритмы обработки сигналов.

Обычно в составе однокристальных аналоговых МП имеется несколько каналов аналого-цифрового и цифро-аналогового преобразования. В аналоговом микропроцессоре разрядность обрабатываемых данных достигает 24 бит и более, большое значение уделяется увеличению скорости выполнения арифметических операций.

Отличительная черта аналоговых микропроцессоров способность к переработке большого объема числовых данных, т. е. к выполнению операций сложения и умножения с большой скоростью при необходимости даже за счет отказа от операций прерываний и переходов. Аналоговый сигнал, преобразованный в цифровую форму, обрабатывается в реальном масштабе времени и передается на выход обычно в аналоговой форме через цифро-аналоговый преобразователь. При этом согласно теореме Котельникова частота квантования аналогового сигнала должна вдвое превышать верхнюю частоту сигнала.

Сравнение цифровых микропроцессоров производится сопоставлением времени выполнения ими списков операций. Сравнение же аналоговых микропроцессоров производится по количеству эквивалентных звеньев аналого-цифровых фильтров рекурсивных фильтров второго порядка. Производительность аналогового микропроцессора определяется его способностью быстро выполнять операции умножения: чем быстрее осуществляется умножение, тем больше эквивалентное количество звеньев фильтра в аналоговом преобразователе и тем более сложный алгоритм преобразования цифровых сигналов можно задавать в микропроцессоре.

Одним из направлений дальнейшего совершенствования аналоговых микропроцессоров является повышение их универсальности и гибкости. Поэтому вместе с повышением скорости обработки большого объема цифровых данных будут развиваться средства обеспечения развитых вычислительных процессов обработки цифровой информации за счет реализации аппаратных блоков прерывания программ и программных переходов.

По характеру временной организации работы микропроцессоры делят на синхронные и асинхронные.

Синхронные микропроцессоры – микропроцессоры, в которых начало и конец выполнения операций задаются устройством управления (время выполнения операций в этом случае не зависит от вида выполняемых команд и величин операндов).

Асинхронные микропроцессоры позволяют начало выполнения каждой следующей операции определить по сигналу фактического окончания выполнения предыдущей операции. Для более эффективного использования каждого устройства микропроцессорной системы в состав асинхронно работающих устройств вводят электронные цепи, обеспечивающие автономное функционирование устройств. Закончив работу над какой-либо операцией, устройство вырабатывает сигнал запроса, означающий его готовность к выполнению следующей операции. При этом роль естественного распределителя работ принимает на себя память, которая в соответствии с заранее установленным приоритетом выполняет запросы остальных устройств по обеспечению их командной информацией и данными.

В зависимости от набора и порядка выполнения команд процессоры делятся на четыре класса:

- Микропроцессоры типа CISC

- Микропроцессоры типа RISC

- Микропроцессоры типа VLIW

- Микропроцессоры типа MISC

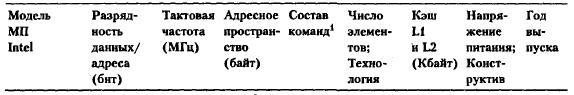

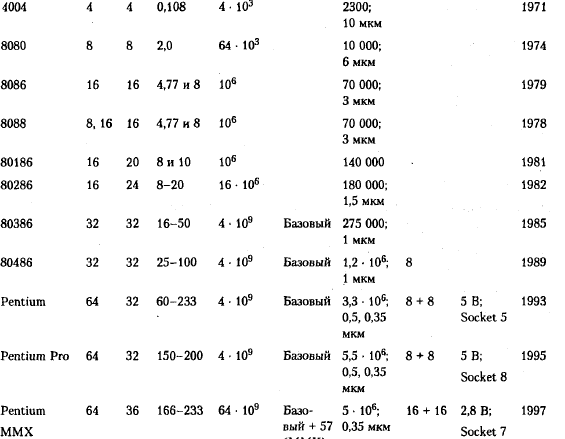

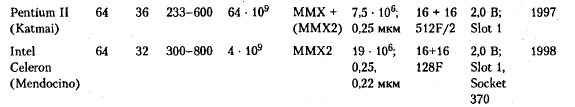

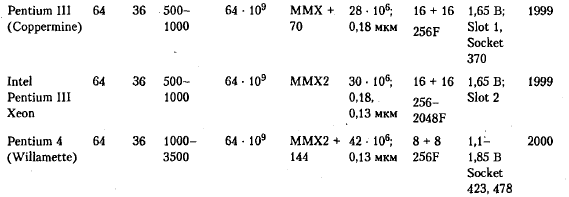

Большинство современных ПК типа IBM PC используют МП типа CISC, выпускаемые многими фирмами: Intel, AMD, Cyrix, IBM и т. д. Законодателем «мод» здесь выступает Intel, но ей «на пятки» наступает AMD, в последние годы создавшая МП по некоторым параметрам лучше «интеловских». Все же пока МП фирмы Intel имеют большее распространение; характеристики некоторых из них приведены в табл.1.

Таблица 1. Характеристики некоторых CISC МП

|

Pentium 4 XE (Gallatine) |

64 |

36 |

3200-3600 |

64⋅109 |

SSE3 |

178⋅106; 0,09 мкм |

16+16 2048F |

Socket LGA 775, Strained, SOI, Cu |

2004 |

|

Pentium D 2 ядра |

34 |

64 |

2800-3200 |

64⋅109 |

SSE3+ |

275⋅106; 0,09 мкм |

16+16 2×1024 |

Socket LGA 775, Strained, SOI, Cu |

2005 |

Условные обозначения в столбце «Состав команд»: «ММХ +» означает, что имеется несколько дополнительных 32-битовых инструкций группы SSE (Streaming SIMD Extention). В столбце кэш символ F у кэш-памяти уровня L2 означает, что память работает на частоте процессора; обозначение F/2 — на половинной частоте процессора.

Пояснения к таблице:

- число элементов — это количество элементарных полупроводниковых переходов, размещенное в интегральной схеме МП. Технология обычно характеризуется размером элемента в микронах (микронная технология).

- микропроцессоры 80486DX и выше имеют встроенный математический сопроцессор, могут работать с умножением внутренней частоты. С увеличенной частотой работают только внутренние схемы МП, все внешние по отношению к МП схемы, в том числе расположенные и на системной плате, работают с обычной частотой;

- у МП 80286 и выше конвейерное выполнение команд — это одновременное выполнение разных тактов последовательных команд в разных частях МП при непосредственной передаче результатов из одной части МП в другую, увеличивает эффективное быстродействие ПК в 2-5 раз;

- у МП 80286 и выше есть возможность работы в вычислительной сети;

- у МП 80286 и выше имеется возможность многозадачной работы (многопрограммность) и сопутствующая ей защита памяти.

Современные микропроцессоры имеют два режима работы:

- реальный (однозадачный, Real Address Mode), в котором возможно выполнение только одной программы и непосредственно адресоваться могут только 1024 + 64 Кбайт основной памяти компьютера, а остальная память (расширенная) доступна лишь при подключении специальных драйверов;

- защищенный (многозадачный, Protected Virtual Address Mode), обеспечивающий выполнение сразу нескольких программ, непосредственную адресацию и прямой доступ (без дополнительных драйверов) к расширенной основной памяти. Предоставляется непосредственный доступ к памяти емкостью 16 Мбайт для МП 286; 4 Гбайт для процессоров 386, 486, Celeron; 100 Гбайт для МП Pentium Xeon и 64 Гбайт для остальных процессоров Pentium, а при страничной организации памяти — к 16 Тбайт виртуальной памяти для каждой задачи. В этом режиме осуществляется автоматическое распределение памяти между выполняемыми программами и соответствующая ее защита от обращений со стороны чужих программ. Защищенный режим поддерживается операционными системами Windows, OS/2, UNIX и т. д.

- в МП 80386 и выше встроена поддержка системы виртуальных машин. Система виртуальных машин является дальнейшим развитием режима многозадачной работы, при котором каждая задача может выполняться под управлением своей операционной системы, то есть практически в одном МП моделируется как бы несколько компьютеров, работающих параллельно и имеющих разные операционные системы;

- у МП 80486 и выше имеется поддержка кэш-памяти;

- у МП 80486 и выше имеются RISC-элементы, позволяющие выполнять короткие операции за 1 такт.

Микропроцессоры 80586 (Р5) более известны по их товарной марке Pentium, которая запатентована фирмой Intel (МП 80586 других фирм имеют иные обозначения: К5 у фирмы AMD, Ml у фирмы Cyrix и т. д.).

МП шестого поколения 80686 (Р6), торговая марка Pentium Pro, имеют более высокую производительность благодаря наличию «динамического исполнения» (dynamic execution).

Это означает:

- наличие многоступенчатой супер конвейерной структуры (superpipelining),

- наличие предсказания ветвлений программы при условных передачах управления (multiple branch prediction)

- исполнение команд по предполагаемому пути ветвления (speculative execution).

В программах решения многих задач содержится большое число условных передач управления. Если процессор может заранее предсказывать направление перехода (ветвления), то производительность его работы значительно повысится за счет оптимизации загрузки вычислительных конвейеров. Если путь ветвления предсказан неверно, процессор должен сбросить полученные результаты, очистить конвейеры и загрузить нужные команды заново, что требует достаточно большого числа тактов. В процессоре Pentium Pro вероятность правильного предсказания 90%, против 80% у МП Pentium.

МП Pentium ММХ (ММХ — MultiMedia eXtention) и Pentium II модернизированы для работы в мультимедийной технологии. В них появилась качественно новая технология: начали внедряться инструкции SIMD (Single Instruction Multiply Data), в которых одно и то же действие совершается над многими данными. Более дешевый вариант Pentium II – Celeron (с отсутствующим либо урезанным до 128 Кбайт кэшем 2-го уровня).

В МП Pentium III присутствует новый блок 128-разрядных регистров, что позволило осуществить расширение набора SIMD-инструкций, ориентированных на форматы данных с плавающей запятой — SSE (Streaming SIMD Extensions). Увеличен кэш 2-го уровня. Pentium III Xeon — процессоры, позиционированные для серверов.

В Pentium 4 улучшена система «динамического исполнения».

Динамическое исполнение позволяет процессору предсказывать порядок выполнения инструкций при помощи технологии множественного предсказания ветвлений, которая прогнозирует прохождение программы по нескольким ветвям. Это оказывается возможным, поскольку в процессе исполнения инструкции процессор просматривает программу на несколько шагов вперед. Технология анализа потока данных позволяет проанализировать программу и составить ожидаемую последовательность исполнения инструкций независимо от порядка их следования в тексте программы. И, наконец, опережающее выполнение повышает скорость работы программы за счет выполнения нескольких инструкций одновременно, по мере их поступления в ожидаемой последовательности — то есть по предположению (интеллектуально). Поскольку выполнение инструкций происходит на основе предсказания ветвлений, результаты сохраняются как «интеллектуальные» с последующим удалением тех, которые вызваны промахами в предсказании. На конечном этапе порядок инструкций и результатов их выполнения восстанавливается до первоначального.

Технология ускоренных вычислений использует два быстрых АЛУ, выполняющие короткие арифметические и логические операции, и третье медленное АЛУ, исполняющее длинные операции (умножение, деление и т. д.).

Используется технология Hyper Treading (tread- поток) – на базе одного МП формируются 2 или более логических процессоров, работающих параллельно. Для задач, позволяющих распараллеливать операции, производительность МП повышается на 30 %.

По мнению специалистов, повышение быстродействия МП путем увеличения тактовой частоты их работы исчерпало себя. Поэтому производительность было решено увеличивать за счет параллельного выполнения вычислений. Появляются многоядерные МП.

Первым представителем двухъядерных МП для ПК в 2005 г. стал PentiumD.

Двухъядерные МП по сравнению с параллельными виртуальными процессорами обеспечивают существенно большую производительность, т. к. у них почти нет совместно используемых процессорных ресурсов (АЛУ, МПП, кэш-память L1 у каждого свои). Потребляемая мощность у них значительно меньше, чем у более высокочастотных однопроцессорных МП той же производительности. Поэтому двух- и многоядерные МП активно используются в ПК. Для двухъядерных МП необходимы системные платы со специальными разъемами и чипсетами.

В феврале 2005 г. компаниями Sony, Toshiba и IBM представлены девятиядерные МП Cell (ячейка). В них используется 0,09 мкм-технология, а также достижения электроники: «кремний на изоляторе» (SOI), «напряженный кремний» (StrainedSi), медные соединения (Cu). Имеют очень низкое энергопотребление (до 80 Вт).

В 2006 г. Intel представила линейку МПCore:

- Core Solo (1 ядро),

- Core Duo, Core 2 Duo, Core 2 Extreme (2 ядра),

- Core 2 Quad (4 ядра),

- Core Penryn (2-4 ядра)

Все МП этой линейки строятся по 65-нанометровой технологии, используют ряд новых энергосберегающих технологий.

В 2008 г. Intel предложила 0,045-микронную архитектуру Nechalem– она использует при построении МП модульность, которая позволяет варьировать количество ядер в МП и изменять насыщенность процессорной системы прочими блоками, в зависимости от назначения и требуемой производительности.

Используют эту архитектуру МП Corei5 иCorei7.Corei5 является несколько облегченным вариантомCorei7. МП Core i3 — по уровню цены и производительности стоят на самой низкой ступени, перед более дорогими и производительными Core i5.

Микропроцессоры типа RISC содержат только набор простых, чаще всего встречающихся в программах команд. При необходимости выполнения более сложных команд в микропроцессоре производится их автоматическая сборка из простых. В этих МП все простые команды имеют одинаковый размер и на выполнение каждой из них тратится 1 машинный такт (на выполнение даже самой короткой команды из системы CISC обычно тратится 4 такта).

Современные 64-разрядные RISC-микропроцессоры выпускаются многими фирмами: Apple (PowerPC), IBM (PPC), DEC (Alpha), HP (PA), Sun (Ultra SPARC) и т. д.

Микропроцессоры типа RISC характеризуются очень высоким быстродействием, но они программно не совместимы с CISC-процессорами: при выполнении программ, разработанных для ПК типа IBM PC, они могут лишь эмулировать (моделировать, имитировать) МП типа CISC на программном уровне, что приводит к резкому уменьшению их эффективной производительности.

Это новый и весьма перспективный тип МП. Микропроцессоры типа VLIW выпускают фирмы Transmeta — это микропроцессор Crusoe моделей ТМ3120, ТМ5400, ТМ5600, Intel — модель Mersed (торговая марка Itanium) и Hewlett-Packard — модель McKinley.

К VLIW-типу можно отнести и МП Elbrus 2000 — E2k, разработанный российской компанией «Эльбрус».

Программисты доступа к внутренним VLIW-командам не имеют: все программы (даже операционная система) работают поверх специального низкоуровневого программного обеспечения (Code Morphing), которое ответственно за трансляцию команд CISC-микропроцессоров в команды VLIW. МП типа VLIW вместо сложной схемной логики, обеспечивающей в современных суперскалярных микропроцессорах параллельное исполнение команд, опираются на программное обеспечение. Упрощение аппаратуры позволило уменьшить габариты МП и потребление энергии (эти МП иногда называют «холодными»).

MISC (minimum instruction set command) – процессор, работающий с минимальным набором длинных команд.

Увеличение разрядности процессоров привело к идее укладки нескольких команд в одно слово (связку, bound) размером 128 бит. Оперируя с одним словом, процессор получил возможность обрабатывать сразу несколько команд. Это позволило использовать возросшую производительность компьютера и его возможность обрабатывать одновременно несколько потоков данных.

Процессор MISC характеризуется небольшим набором чаще всего встречающихся команд. Вместе с этим принцип команд VLIM обеспечивает выполнение группы команд за один цикл работы процессора. Порядок выполнения команд распределяется таким образом, чтобы в максимальной степени загрузить маршруты, по которым проходят потоки данных. Таким образом, архитектура MISC объединила вместе суперскалярную (многопоточную) и VLIM концепции. Компоненты процессора просты и работают с высокими скоростями.

Физическая и функциональная структура микропроцессора

В состав микропроцессора Pentium обычно входят следующие физические компоненты:

- Core — ядро МП;

- Execution Unit — исполняющий модуль;

- IntegerALU— АЛУ для операций с целыми числами (с фиксированной запятой);

- Registers — регистры;

- Floating Point Unit — блок для работы с числами с плавающей запятой;

- Primary Cache — кэш первого уровня, в том числе кэш данных (Data Cache) и кэш команд (Code Cache);

- Instruction Decode and Prefetch Unit и Branch Predictor — блоки декодирования инструкций, опережающего их исполнения и предсказания ветвлений;

- Bus Interface — интерфейсные шины, в том числе 64- и 32-битовая шины, и выход на системную шину к оперативной памяти (То RAM).

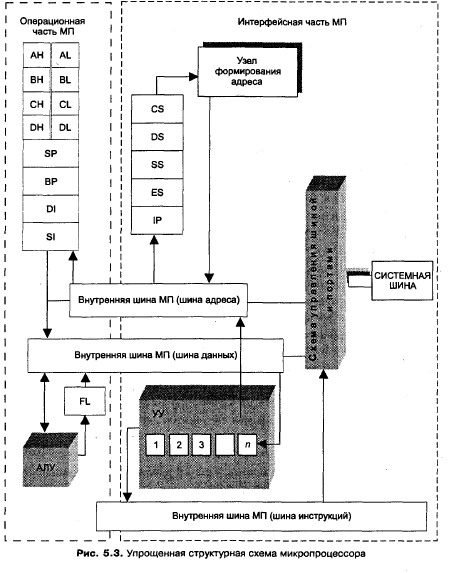

Функционально МП можно разделить на две части:

- операционную, содержащую устройство управления (УУ), арифметико-логическое устройство (АЛУ) и микропроцессорную память (МПП) (за исключением нескольких адресных регистров);

- интерфейсную, содержащую адресные регистры МПП; блок регистров команд — регистры памяти для хранения кодов команд, выполняемых в ближайшие такты; схемы управления шиной и портами.

Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из памяти (ее запись в блок регистров команд и предварительный анализ) происходит во время выполнения операционной частью предыдущей команды. Современные микропроцессоры имеют несколько групп регистров в интерфейсной части, работающих с различной степенью опережения, что позволяет выполнять операции в конвейерном режиме. Такая организация МП позволяет существенно повысить его эффективное быстродействие.

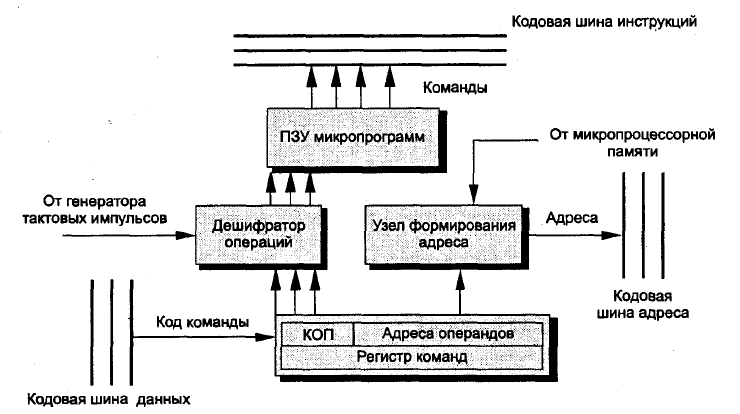

Устройство управления (УУ) является функционально наиболее сложным устройством ПК — оно вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций (КШИ) во все блоки машины. Упрощенная функциональная схема УУ показана на рис. 1. На рисунке представлены:

- регистр команд — запоминающий регистр, в котором хранится код команды — код выполняемой операции (КОП) и адреса операндов, участвующих в операции. Регистр команд расположен в интерфейсной части МП, в блоке регистров команд;

- дешифратор операций — логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов;

- постоянное запоминающее устройство (ПЗУ) микропрограмм хранит в своих ячейках управляющие сигналы (импульсы), необходимые для выполнения в блоках ПК процедур обработки информации. Импульс по выбранному дешифратором операций в соответствии с кодом операции проводу считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов;

- узел формирования адреса (находится в интерфейсной части МП) — устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров МПП;

- кодовые шины данных, адреса и инструкций — часть внутренней интерфейсной шины микропроцессора.

В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур:

- выборка из регистра-счетчика адреса команды МПП адреса ячейки ОЗУ, где хранится очередная команда программы;

- выборка из ячеек ОЗУ кода очередной команды и приема считанной команды в регистр команд;

- расшифровка кода операции и признаков выбранной команды;

- считывание из соответствующих расшифрованному коду операции ячеек ПЗУ микропрограмм управляющих сигналов (импульсов), определяющих во всех блоках машины процедуры выполнения заданной операции, и пересылка управляющих сигналов в эти блоки;

- считывание из регистра команд и регистров МПП отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов;

- выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов;

- запись результатов операции в память;

- формирование адреса следующей команды программы.

Рис. 1. Укрупненная функциональная схема УУ

Арифметико-логическое устройство

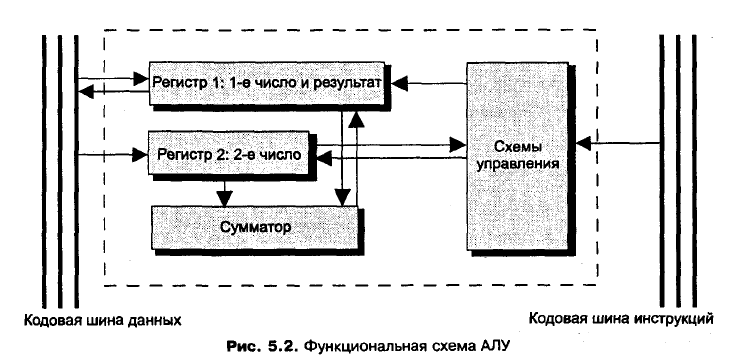

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. Функционально АЛУ (рис. 2) состоит обычно из двух регистров, сумматора и схем управления (местного устройства управления).

Сумматор — вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова.

Регистры — быстродействующие ячейки памяти различной длины: регистр 1 имеет разрядность двойного слова, а регистр 2 — разрядность слова. При выполнении операций в регистр 1 помещается первое число, участвующее в операции, а по завершении операции — результат; в регистр 2 — второе число, участвующее в операции (по завершению операции информация в нем не изменяется). Регистр 1 может и принимать информацию с кодовых шин данных и выдавать информацию на них; регистр 2 только получает информацию с этих шин.

Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ.

АЛУ выполняет арифметические операции «+», «-», «х» и «> только над двоичной информацией с запятой, фиксированной после последнего разряда, то есть только над целыми двоичными числами. Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется с привлечением математического сопроцессора или по специально составленным программам.

Рассмотрим в качестве примера выполнение команды умножения. Перемножаются числа 1101 и 1011 (числа для простоты взяты 4-битовыми). Множимое находится в регистре 1, имеющем удвоенную по отношению к регистру 2 разрядность; множитель размещается в регистре 2. Операция умножения требует для своего выполнения нескольких тактов. В каждом такте число из регистра 1 проходит в сумматор (имеющий также удвоенную разрядность) только в том случае, если в младшем разряде регистра 2 находится 1. В данном примере в первом такте число 1101 пройдет в сумматор, и в этом же первом такте число в регистре 1 сдвигается на 1 разряд влево, а число в регистре 2 — на 1 разряд вправо. В конце такта после сдвигов в регистре 1 будет находиться число 11010, а в регистре 2 — число 101. Во втором такте число из регистра 1 пройдет в сумматор, так как младший разряд в регистре 2 равен 1; в конце такта числа в регистрах опять будут сдвинуты влево и вправо, так, что в регистре 1 окажется число 110100, а в регистре 2 — число 10. В третьем такте число из регистра 1 не пройдет в сумматор, так как младший разряд в регистре 2 равен 0; в конце такта числа в регистрах будут сдвинуты влево и вправо, так что в регистре 1 окажется число 1101000, а в регистре 2 — число 1. На четвертом такте число из регистра 1 пройдет в сумматор, поскольку младший разряд в регистре 2 равен 1; в конце такта числа в регистрах будут сдвинуты влево и вправо, так что в регистре 1 окажется число 11010000, а в регистре 2 — число 0. Поскольку множитель в регистре 2 стал равным 0, операция умножения заканчивается. В результате в сумматор последовательно поступят и будут сложены числа: 1101, 11010, 1101000; их сумма 10001111 (143 в десятичной системе) и будет равна произведению чисел 1101 х 1011 (13 х 11 десятичные).

Рис. 2. Функциональная схема АЛУ

Микропроцессорная память

Микропроцессорная память (МПП) базового МП 8088 включает в себя 14 двухбайтовых запоминающих регистров. У МП 80286 и выше имеются дополнительные регистры, например, у МП типа VLIW есть 256 регистров, из которых 128 — регистры общего назначения. У МП 80386 и выше некоторые регистры, в том числе и регистры общего назначения, — 4-байтовые (у МП Pentium есть и восьмибайтовые регистры). Но в качестве базовой модели, в частности для языка программирования ассемблер и отладчика программ Debug, используется 14-ре-гистровая система МПП. Все регистры можно разделить на 4 группы:

- универсальные регистры: АХ, ВХ, СХ, DX;

- сегментные регистры: CS, DS, SS, ES;

- регистры смещения: IP, SP, BP, SI, DI;

- регистр флагов: FL.

Если регистры 4-байтовые или 8-байтовые, их имена несколько изменяются, например 4-байтовые универсальные регистры АХ, ВХ, СХ, DX именуются соответственно ЕАХ, ЕВХ, ЕСХ, EDX. При этом если используется их двухбайтовая или однобайтовая часть, наименования этих частей регистров соответствуют рассматриваемым ниже.

Регистры АХ, ВХ, СХ и DX являются универсальными (их часто называют регистрами общего назначения — РОН); каждый из них может использоваться для временного хранения любых данных, при этом позволено работать с каждым регистром целиком, а можно отдельно и с каждой его половиной (регистры АН, ВН, СН, DH — старшие (High) байты, а регистры AL, BL, CL, DL — младшие (Low) байты соответствующих 2-байтовых регистров). Но каждый из универсальных регистров может использоваться и как специальный при выполнении некоторых конкретных команд программы. В частности:

- регистр АХ — регистр-аккумулятор, через его порты осуществляется ввод-вывод данных в МП, а при выполнении операций умножения и деления АХ используется для хранения первого числа, участвующего в операции (множимого, делимого), и результата операции (произведения, частного) после ее завершения;

- регистр ВХ часто используется для хранения адреса базы в сегменте данных и начального адреса поля памяти при работе с массивами;

- регистр СХ — регистр-счетчик, используется как счетчик числа повторений при циклических операциях;

- регистр DX используется как расширение регистра-аккумулятора при работе с 32-разрядными числами и при выполнении операций умножения и деления, используется для хранения номера порта при операциях ввода-вывода и т. д.

Регистры сегментной адресации CS, DS, SS, ES используются для хранения начальных адресов полей памяти (сегментов), отведенных в программах для хранения:

- команд программы (сегмент кода — CS);

- данных (сегмент данных — DS);

- стековой области памяти (сегмент стека — SS);

- дополнительной области памяти данных при межсегментных пересылках (расширенный сегмент — ES), поскольку размер сегмента в реальном режиме работы МП ограничен величиной 64 Кбайт.

Регистры смещений (внутрисегментной адресации) IP, SP, BP, SI, DI предназначены для хранения относительных адресов ячеек памяти внутри сегментов (смещений относительно начала сегментов):

- регистр IP (Instruction Pointer) хранит смещение адреса текущей команды программы;

- регистр SP (Stack Pointer) — смещение вершины стека (текущего адреса стека);

- регистр BP (Base Pointer) — смещение начального адреса поля памяти, непосредственно отведенного под стек;

- регистры SI, DI (Source Index и Destination Index соответственно) предназначены для хранения адресов индекса источника и приемника данных при операциях над строками и им подобных.

Регистр флагов FL содержит условные одноразрядные признаки-маски, или флаги, управляющие прохождением программы в ПК; флаги работают независимо друг от друга, и лишь для удобства они помещены в единый регистр. Всего в регистре содержится 9 флагов: 6 из них статусные, отражают результаты операций, выполненных в компьютере (их значения используются, например, при выполнении команд условной передачи управления — команд ветвления программы), а 3 других — управляющие, непосредственно определяют режим исполнения программы.

Статусные флаги:

- CF (Carry Flag) — флаг переноса. Содержит значение «переносов» (0 или 1) из старшего разряда при арифметических операциях и некоторых операциях сдвига и циклического сдвига;

- PF (Parity Flag) — флаг четности. Проверяет младшие восемь битов результатов операций над данными. Нечетное число единичных битов приводит к установке этого флага в 0, а четное — в 1;

- AF (Auxiliary Carry Flag) — флаг логического переноса в двоично-десятичной арифметике. Вспомогательный флаг переноса устанавливается в 1, если арифметическая операция приводит к переносу или заему четвертого справа бита однобайтового операнда. Этот флаг используется при арифметических операциях над двоично-десятичными кодами и кодами ASCII;

- ZF (Zero Flag) — флаг нуля. Устанавливается в 1, если результат операции равен нулю; если результат не равен нулю, ZF обнуляется;

- SF (Sign Flag) — флаг знака. Устанавливается в соответствии со знаком результата после арифметических операций: положительный результат устанавливает флаг в 0, отрицательный — в 1;

- OF (Overflow Flag) — флаг переполнения. Устанавливается в 1 при арифметическом переполнении: если возник перенос в знаковый разряд при выполнении знаковых арифметических операций, если частное от деления слишком велико и переполняет регистр результата и т. д.

Управляющие флаги:

- TF (Trap Flag) — флаг системного прерывания (трассировки). Единичное состояние этого флага переводит процессор в режим пошагового выполнения программы (режим трассировки);

- IF (Interrupt Flag) — флаг прерываний. При нулевом состоянии этого флага прерывания запрещены, при единичном — разрешены;

DF (Direction Flag) — флаг направления. Используется в строковых операциях для задания направления обработки данных. При нулевом состоянии флага команда увеличивает содержимое регистров SI и DI на единицу, обусловливая обработку строки «слева направо»; при единичном — «справа налево».

Интерфейсная часть МП предназначена для связи и согласования МП с системной шиной ПК, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд. Интерфейсная часть включает в свой состав:

- адресные регистры МПП;

- узел формирования адреса;

- блок регистров команд, являющийся буфером команд в МП;

- внутреннюю интерфейсную шину МП;

- схемы управления шиной и портами ввода-вывода.

Некоторые из названных устройств, такие как узел формирования адреса и регистр команды, непосредственно выполняемой МП, функционально входят в состав устройства управления.

Порты ввода-вывода — это пункты системного интерфейса ПК, через которые МП обменивается информацией с другими устройствами. Всего портов у МП может быть 65 536 (равно количеству разных адресов, которые можно представить числом формата «слово»). Каждый порт имеет адрес — номер порта; по существу это адрес ячейки памяти, являющейся частью устройства ввода-вывода, использующего этот порт, а не частью основной памяти компьютера.

Порту устройства соответствуют аппаратура сопряжения и два регистра памяти — для обмена данными и управляющей информацией. Некоторые внешние устройства используют и основную память для хранения больших объемов информации, подлежащей обмену. Многие стандартные устройства (НЖМД, НГМД, клавиатура, принтер, сопроцессор и т. д.) имеют постоянно закрепленные за ними порты ввода-вывода.

Схема управления шиной и портами выполняет следующие функции: .

- формирование адреса порта и управляющей информации для него (переключение порта на прием или передачу и т. д.);

- прием управляющей информации от порта, информации о готовности порта и его состоянии;

- организация сквозного канала в системном интерфейсе для передачи данных между портом устройства ввода-вывода и МП.

Схема управления шиной и портами использует для связи с портами кодовые шины инструкций, адреса и данных системной шины: при доступе к порту МП посылает сигнал по кодовой шине инструкций (КШИ), который оповещает все устройства ввода-вывода, что адрес на кодовую шину адреса (КША) является адресом порта, а затем посылает и сам адрес порта. Устройство с совпадающим адресом порта дает ответ о готовности. После чего по кодовой шине данных (КШД) осуществляется обмен данными.

Рис. 3. Упрощенная структурная схема микропроцессора

Заключение

В последние годы произошли кардинальные изменения в области вычислительной техники. Благодаря разработке и внедрению микропроцессоров в структуру ЭВМ появились малогабаритные, удобные для пользователя персональные компьютеры и в роли пользователя может быть не только специалист по вычислительной технике, но и любой человек.

Однако процесс повышения быстродействия микропроцессорных устройств идет неуклонно вперед и в настоящее время существуют микропроцессоры, минимальное время выполнения команды у которых достигает 5 нс. С помощью современных микропроцессоров уже сегодня возможно создавать системы управления с полосой пропускания в десятки и даже сотни Кгц. В свою очередь, аналоговые системы несмотря на практически мгновенное протекание сигналов также обладают конечным быстродействием из-за не идеальности компонентов и наличия паразитных реактивных связей в системе. Временные параметры цифровых систем, в отличие от аналоговых, не изменяются с течением времени и не зависят от внешних факторов.

Таким образом, в настоящее время, благодаря всему вышеперечисленному идет полномасштабное внедрение микропроцессорной техники практически во все сферы деятельности, где еще вчера господствовали аналоговые методы обработки информации.

В современной преобразовательной технике микроконтроллеры выполняют не только роль непосредственного управления полупроводниковым преобразователем за счет встроенных специализированных периферийных устройств, но и роль цифрового регулятора, системы защиты и диагностики, а также системы связи с технологической сетью высшего уровня.

Список источников:

- Толковый словарь по вычислительным системам / Под ред. В. Иллингуорта и др. — М.: Машиностроение, 1989. 568 с. ISBN 5-217-00617-X (перевод словаря издательства Oxford University Press)

- Back to the Moon: The Verification of a Small Microprocessor's Logic Design Архивная копия от 11 октября 2011 на Wayback Machine - NASA Office of Logic Design

- ↑ Rick Hodgin. Six fold reduction in semiconductor power loss, a faster, lower heat process technology. TG Daily.

- В.Л. Горбунов, Д.И. Памфилов, Д.Л. Преснухин. Микропроцессоры. 04. Основы построения микро-ЭВМ / под ред. Л.Н. Преснухина. — М.: Высшая школа, 1984. — К580, К589, К587 и К588

- А. В. Бесекерский, Ефимов Н. Б., Зиатдинов С. И. и др. 4.3 Области применения и состав микропроцессорного комплекта К1804 // Микропроцессорные системы автоматического управления. — М.: «Машиностроение», 1988. — ISBN 5-217-00176-3.

- Нефедов А. В, Савченко А. М., Феоктистов Ю. Ф. Под редакцией Широкова Ю. Ф. Раздел 3. Цифровые интегральные микросхемы и их электрические параметры // Зарубежные интегральные микросхемы для промышленной электронной аппаратуры: Справочник. — М.: Энергоатомиздат, 1989. — 288 с. — ISBN 5-283-01540-8.

- Под ред. Шахнова В.А.,. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник. В двух томах. Том 1.. — М.: «Радио и Связь», 1988. — 368 с. — ISBN 5-256-00372-0.

- Под ред. Шахнова В.А.,. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник. В двух томах. Том 2.. — М.: «Радио и Связь», 1988. — 368 с. — ISBN 5-256-00373-9.

- Борисов В. С., Власов Ф. С., Сержанович Д. С., Сухопаров А. И. Микропроцессорные комплекты БИС на основе интегральной инжекционной логики / Под редакцией Калошкина Э. П.. — М.: «Радио и Связь», 1984. — 246 с.

- Adam Osborne. An Introduction to Microcomputers. — 2nd Ed. — Berkely (California): Osborne-McGraw Hill, 1980. — P. 1-1. — ISBN 0-931988-34-9.

- Ray, A. K. Advanced Microprocessors and Peripherals / A. K. Ray, Bhurchand. — India : Tata McGraw-Hill.

- Intel's New Brand Structure Explained. Technology@Intel. Intel Corporation (17.06.2009).

- Intel® Core™ Duo Processor // intel.com

- Intel® Core™ Solo Processor: T1000 Series / U1000 Series // intel.com

- ОРГАНЫ ИСПОЛНИТЕЛЬНОЙ ВЛАСТИ (Понятие, признаки и принципы построения исполнительной власти в Российской Федерации)

- ОРГАНЫ ИСПОЛНИТЕЛЬНОЙ ВЛАСТИ (Правительство России как федеральный орган исполнительной власти)

- Корпоративная культура в организации (ООО «БПО Сервис»)

- Организационная культура и ее роль в современных организациях (ООО Телекомпании «4 канал»)

- Организация учёта и контроля за оптовыми закупками

- Процессы принятия решений в организации (ООО «Макдоналдс»)

- Управление поведением в конфликтных ситуациях (Основные методы диагностики и профилактики конфликтов)

- Проблемы профессиональных стрессов.Профессиональное выгорание (педагог)

- Мотивация персонала и проектирование систем стимулирования труда (педагоги)

- Невербальные проявления эмоциональных состояний человека (Особенности невербального проявления эмоциональных состояний человека)

- Менеджмент как организационно-целевое управление (ООО «Elermet»)

- Проектирование реализации операций бизнес-процесса «Расчет заработной платы» (ПАО «ВиИнСи»)