Назначение и структура процессора персонального компьютера

Содержание:

Введение

Для того, что бы грамотно выбрать персональный компьютер надо знать его строение и новейшие тенденции в разработки компьютеров. Центральное процессорное устройство – основа персонального компьютера. От его выбора зависит быстродействие работы компьютера и функции, которые он может выполнить.

Объектом исследования является процессор персонального компьютера.

Предмет исследования его назначение, функции и характеристики.

Целью курсовой работы является проведение анализа процессоров персонального компьютера.

В курсовой работе решаются задачи:

- Исследовать назначения и структуру процессора персонального компьютера.

- Проанализировать функции процессора персонального компьютера.

- Провести классификацию процессоров персонального компьютера.

Результаты исследований в дальнейшем будут использоваться для написания дипломного проекта.

Глава 1. Назначение и структура процессора персонального компьютера

Процессор или центральное процессорное устройство является основным элементом электронно-вычислительной машины (компьютера) [1, 2, 3]. Процессор выполняет все функции по преобразованию данных: сложение, вычитание, сдвиг, логические операции и т.д.

Вначале персональные компьютеры имели один процессор, потом появился сопроцессор для обработки операций с числами с плавающей запятой, что существенно ускорило обработку вещественных чисел. В различных конфигурациях компьютеров может быть несколько процессоров (ядер) [3, 4, 5].

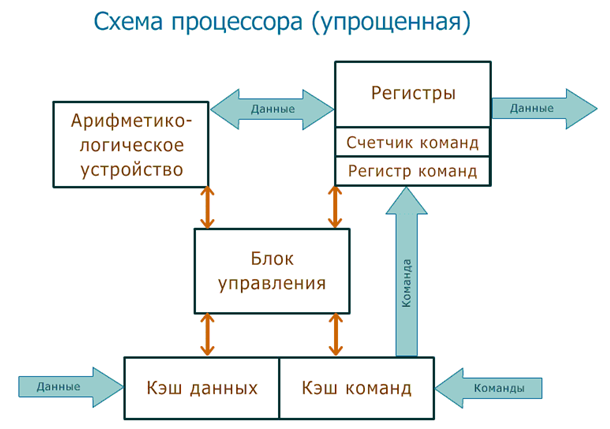

Основными частями процессора являются арифметико-логическое устройство, регистры и устройство управления [6, 7, 8, 23].

Арифметико-логическое устройство выполнят основные математические и логические операции (Рис.1.). Все вычисления производятся в двоичной системе счисления. От устройства управления зависит согласованность работы частей самого процессора и его связь с другими (внешними для него) устройствами. В регистрах временно хранятся текущая команда, исходные, промежуточные и конечные данные (результат вычислений арифметико-логическое устройство). Разрядность всех регистров одинакова.

Кэш данных и команд хранит часто используемые данные и команды. Обращение в кэш происходит намного быстрее, чем в оперативную память, поэтому, чем он больше, тем лучше.

Рис. 1. Упрощённая схема процессора.

Работает процессор под управлением программы, находящейся в оперативной памяти. Арифметико-логическое устройство, получив данные и команду, выполняет указанную операцию и записывает результат в один из свободных регистров.

Текущая команда находится в специально для нее отведенном регистре команд. В процессе работы с текущей командой увеличивается значение так называемого счетчика команд, который теперь указывает на следующую команду (если, конечно, не было команды перехода или останова).

Часто команду представляют как структуру, состоящую из записи операции (которую требуется выполнить) и адресов ячеек исходных данных и результата. По адресам указанным в команде берутся данные и помещаются в обычные регистры (в смысле не в регистр команды), получившийся результат тоже сначала оказывается в регистре, а уж потом перемещается по своему адресу, указанному в команде [9, 10, 11].

.

Тактовая частота процессора на сегодняшний день измеряется в гигагерцах (ГГц), Ранее измерялось в мегагерцах (МГц). 1МГц = 1 миллиону тактов в секунду [12, 13].

Процессор связан с другими устройствами (оперативной памятью) с помощью шин данных, адреса и управления. Разрядность шин всегда кратна 8 (понятно почему, если мы имеем дело с байтами), изменчива в ходе исторического развития компьютерной техники и различна для разных моделей, а также не одинакова для шины данных и адресной шины.

Разрядность шины данных говорит о том, какое количество информации (сколько байт) можно передать за раз (за такт). От разрядности шины адреса зависит максимальный объем оперативной памяти, с которым процессор может работать вообще.

На мощность (производительность) процессора влияют не только его тактовая частота и разрядность шины данных, также важное значение имеет объем кэш-памяти.

Глава 2. Функции процессора персонального компьютера

Основные функции любого процессора следующие [14, 15, 16, 17]:

выборка (чтение) выполняемых команд;

ввод (чтение) данных из памяти или устройства ввода/вывода;

вывод (запись) данных в память или в устройства ввода/вывода;

обработка данных (операндов), в том числе арифметические операции над ними;

адресация памяти, то есть задание адреса памяти, с которым будет производиться обмен;

обработка прерываний и режима прямого доступа.

Большинство современных процессоров для персональных компьютеров, в общем, основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом [18, 19, 20].

Этапы цикла выполнения:

Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения;

Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности;

Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её;

Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды;

Снова выполняется п. 1.

Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло название устройства).

Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм работы процессора. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода - тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки прерывания.

Команды центрального процессора являются самым нижним уровнем управления компьютером, поэтому выполнение каждой команды неизбежно и безусловно. Не производится никакой проверки на допустимость выполняемых действий, в частности, не проверяется возможная потеря ценных данных. Чтобы компьютер выполнял только допустимые действия, команды должны быть соответствующим образом организованы в виде необходимой программы.

Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие ритмом для центрального процессора. Частота тактовых импульсов называется тактовой частотой.

Глава 3. Классификация процессоров персонального компьютера

В технической литературе, пресс-релизах, а также в предварительных анонсах разработчиков и производителей нередко используются кодовые наименования процессоров и их архитектур. Однако после официального объявления эти же изделия становятся известны уже под другими именами. При этом из маркетинговых соображений процессорам, созданным по разной технологии и имеющим отличия в архитектуре своих ядер, часто присваиваются одинаковые имена. Такое положение вещей дезорганизует не только начинающих пользователей, но нередко и специалистов.

Ниже представлена попытка классификации и расшифровки фирменных (торговых марок) и кодовых имен процессоров, а также их ядер с приведением кратких характеристик. В качестве основы использована статья с добавлением материалов, опубликованных на сайтах и в фирменной документации производителей [21, 22, 23].

3.1.Процессоры Интел Пентиум

Intel Pentium – появились в 1993 году.(Рис.2.). Первое поколение Pentium носило кодовое имя P5, а также i80501, напряжение питания было 5 В.

Рис. 2. Процессор Интел Пентиум

В 1997 году появились Pentium MMX. Добавился новый набор из 57 команд MMX. Технология – 0,35 мкм. Напряжение питания ядра уменьшилось до 2,8 В.

В ноябпе 1995 года выпустили Pentium Pro –процессоры шестого поколения. Впервые применена кэш-память L2, объединенная в одном корпусе с ядром и работающая на частоте ядра процессора.

В мае 1997 года вышло семейство Pentium II/III .

Pentium II (Klamath, Deschutes, Katmai) предназначено для массового рынка ПК среднего уровня,

Celeron (Covington, Mendocino, Dixon и т.д.) – для недорогих компьютеров,

Xeon (Xeon, Tanner, Cascades и т.д.) – для высокопроизводительных серверов и рабочих станций.

В 1998 году появилось семейство процессоров Celeron для недорогих компьютеров

Dixon – наименование ядра, а также кодовое имя процессоров, ориентированных на применение в портативных компьютерах. Технология – 0,25 мкм, в дальнейшем – 0,18 мкм. Объем кэш-памяти первого уровня – 32 Кбайта. Как и в Mendocino, кэш-память L2 расположена на чипе, однако ее объем увеличен до 256 Кбайт. Тактовая частота – 300-500 МГц, частота шины – 66 МГц. Официальная классификация – мобильные процессоры Pentium II.

Coppermine – наименование ядра процессоров Pentium III и Celeron. Технология – 0,18 мкм. Характеризуется наличием интегрированных на чипах процессоров 256 Кбайт кэш-памяти L2 для Pentium III и 128 Кбайт – для Celeron. Частота – от 533 МГц и выше. Наряду с FSB100 МГц версиями Pentium III выпущены и варианты FSB133 МГц. Последние процессоры, рассчитанные на Slot 1, постепенно были вытеснены изделиями в конструктиве FC-PGA 370, рассчитанными на разъем Socket 370. Частота шины для процессоров Celeron – 66 МГц, а начиная с модели Celeron 800 – 100 МГц. Напряжение питания ядра – от 1,5 В до 1,7 В.

Coppermine T – наименование ядра процессоров Pentium III и Celeron. Является переходной ступенью от ядра архитектуры Coppermine к ядру архитектуры Tualatin. Создан по технологии 0,18 мкм. Ориентирован на работу с чипсетами, поддерживающими процессоры с ядром Tualatin.

В 2003 году выпустили процессоры Banias. В чип интегрированы вычислительное ядро процессора, графическое ядро, а также северный мост чипсета.

Xeon – официальное наименование линейки процессоров, ориентированных на использование в составе мощных серверов и рабочих станций.

Первые варианты были построены на ядре Deschutes. Являются заменой процессоров Pentium Pro. Технология – 0,25 мкм. Процессорный разъем Slot 2. Процессоры этого типа способны работать в мультипроцессорных конфигурациях. Кэш-память L2 имеет объем 512, 1024, 2048 Кбайт, что во многом определяет высокую стоимость и тепловыделение.

Принципиально новые компьютеры получили название Pentium 4.

К этой серии относятся процессоры Willamette и Northwood.

Рис. 3. Процессор AMD

K5 – первые процессоры AMD, анонсированные в качестве конкурента Pentium. Разъем – Socket 7. Подобно Cyrix 6x86, использовали PR-рейтинг с показателями от 75 до 166 МГц. При этом используемая частота системной шины составляла от 50 до 66 МГц. Кэш-память L1 – 24 Кбайт (16 Кбайт для инструкций и 8 Кбайт для данных). Кэш-память L2 расположена на материнской плате и работает на частоте процессорной шины. К5 степпинг 0 имел кодовое имя "SSA5", а у степпингов 1, 3, 5 было кодовое имя "5k86". Стоит отметить, что до 5k86 существовал процессор AMD 5x86-P75, где P75 это рейтинг, а реальная частота была его была 133 МГц (33 x 4), процессор была рассчитан под Socket 5.

K6 – процессоры, анонсированные в качестве конкурента Pentium II. Первые модели производились по технологии 0,35 мкм, в дальнейшем – 0,25 мкм (кодовое имя "Little Foot"). Процессоры работали на частоте от 166 до 233 МГц. Были созданы на базе дизайна процессора 686 от приобретенной AMD компании NexGen. По сравнению со своими предшественниками получили модуль MMX, увеличился объем кэша L1 – до 64 Кбайт (по 32 Кбайт для инструкций и данных).

K6-2 – следующее поколение K6 с кодовым именем "Chomper". Процессор вышел в мае 1998 года, основным усовершенствованием является поддержка дополнительного набора инструкций 3DNow! и частоты системной шины 100 МГц. Кэш-память L1 – 64 Кбайт (по 32 Кбайт для инструкций и данных), кэш L2 находится на материнской плате и может иметь объем от 512 Кбайт до 2 Мбайт, работая на частоте шины процессора. Первые модели имели частоту ядра 266 МГц.

K6-2+ – одни из последних Socket 7 процессоров AMD. И первые Socket 7 процессоры, сделанные с использованием 0,18 мкм техпроцесса.

K6-III (Sharptooth) – первые процессоры от AMD, имеющие кэш-память L2, объединенную с ядром. Последние процессоры, сделанные под платформу Socket 7. Фактически, представляют собой просто K6-2 с 256 Кбайт кэш-памятью L2 на чипе, работающей на той же частоте, что и ядро процессора. Кэш-память L1 имеет объем 64 Кбайт (по 32 Кбайт для инструкций и данных), кэш-память L3 находится на материнской плате и может иметь объем от 512 Кбайт до 2 Мбайт, работая на частоте шины процессора. Первые модели, выпущенные в феврале 1999 года, были рассчитаны на 400 и 450 МГц.

Argon – кодовое название использованного в K7 ядра.

K7 – первые процессоры, архитектура и интерфейс которых отличаются от Intel. Объем кэш-памяти L1 – 128 Кбайт (по 64 Кбайт для инструкций и данных). Кэш-память L2 – 512 Кбайт, работающая на 1/2, 2/5 или 1/3 частоты процессора. Процессорная шина – Alpha EV-6. Тактовая частота шины – 100 МГц с передачей данных при 200 МГц. Поддерживаемые наборы инструкций – MMX и расширенный по сравнению с K6-III набор 3DNow!. Форм-фактор – Slot A. Получил наименование Athlon. Были выпущены модели 500-1000 МГц. Ядро K75 – алюминиевые соединения, K76 – медные.

Magnolia – кодовое название 1 ГГц Athlon с ядром K76 до его выхода.

Thunderbird – наименование ядра процессоров Athlon, выпущенных по технологии 0,18 мкм с использованием технологии медных соединений. На чипе интегрированы 256 Кбайт полноскоростного exclusive кэша L2. В качестве переходного варианта некоторое время выпускался в форм-факторе Slot A. Однако основным форм-фактором является Socket A. Модель с частотой 1,33 ГГц демонстрирует большую производительность на офисных задачах, чем процессор Intel Pentium 4 с частотой 1,7 ГГц. Технологический потенциал ядра Thunderbird предоставляет возможность выпуска изделий с частотой до 1,5 ГГц.

Athlon – наименование процессоров, созданных на основе архитектур K7, К75, К76, Thunderbird в вариантах Slot A и Socket A (Socket 462). Высокопроизводительные процессоры, ориентированные на сектор компьютеров High-End.

Athlon XP – наименование процессоров, созданных на основе ядра Palomino, Socket A (Socket 462).

Duron – наименование линейки процессоров, ориентированных на сектор компьютеров Low-End. Являются конкурентами процессоров Celeron, однако обладают меньшей ценой и большей производительностью при равных рабочих частотах. Построены на варианте ядра Thunderbird с урезанной до 64 Кбайт кэш-памятью L2. Выпускаются только в форм-факторе Socket A.

Spitfire – кодовое наименование ядра и процессоров Duron.

Mustang – серверный вариант Athlon. Кэш-память L2 – 1-2 Мбайт, интегрированная в чип процессора. Процессор рассчитан на использование шины 266 МГц и памяти DDR SDRAM. Выпуск отменен.

Corvette – кодовое наименование мобильного варианта ядра Mustang. Переименован в Palomino.

Palomino – кодовое наименование ядра процессоров Athlon, пришедшего на смену архитектуре Thunderbird. Предполагаются незначительные архитектурные изменения с целью улучшения скоростного потенциала процессора. Например, в составе ядра используются улучшенный блок предсказания ветвлений и аппаратная предварительная выборка из памяти. Процессоры на новом ядре не будут поддерживать SSE2. Информация о том, что конвейер в ядре Palomino будет содержать большее число ступеней, не подтверждается. Palomino будет быстрее, чем Thunderbird, работающий на той же частоте; используя этот факт AMD ввела новый рейтинг на основе разработанной технологии QuantiSpeed, по которому, например 1,733 МГц процессор Athlon XP получил рейтинг 2100+. Socket A останется основным процессорным гнездом еще на 2-3 года, фирма AMD не намерена менять физический интерфейс своих процессоров. Palomino будет работать на материнских платах, поддерживающих шину EV6 с частотой 266 МГц. В производстве процессоров будет использована технология медных соединений. Младшие модели рассчитаны на тактовую частоту ядра 1,533 ГГц и выше.

Morgan – кодовое наименование ядра процессоров Duron. Отличается от Palomino не только объемом L2, но и тем, что будет производиться по технологии с использованием алюминиевых соединений.

Thoroughbred – улучшенная версия Palomino, созданная по технологии 0,13 мкм. Предполагаемая тактовая частота – 2 ГГц. Срок выхода – 2002 г.

Appaloosa – улучшенная версия Morgan, созданная по технологии 0,13 мкм. Срок выхода – 2002 г.

Barton – версия Thoroughbred, улучшенная использованием технологии SOI (SOI – silicon-on-insulator – "кремний-на-изоляторе"). Использование этой технологии позволяет увеличить тактовые частоты приблизительно на 20% и уменьшить при этом энергопотребление.

Hammer – семейство 64-разрядных процессоров. В него входят ClawHammer и SledgeHammer. Семейство 64-разрядных процессоров Hammer базируется на архитектуре K7, в которую добавлены 64-разрядные регистры и дополнительные инструкции для работы с этими регистрами, а также новые серверные инструкции. Возможно использование технологии SOI. Решается вопрос о поддержке SSE2.

ClawHammer – первый 64-разрядный процессор AMD. В отличие от Itanium, этот процессор будет ориентирован главным образом на 32-разрядные инструкции. Одновременно с его выходом ожидается появление новой шины HyperTransport (Lightning Data Transport – LDT), используемой для связи с процессорами и устройствами ввода/вывода. LDT должна стать не заменой, а дополнением к системной шине EV6 или EV7. Обеспечена поддержка до двух процессоров. Предполагаемая скорость – 2 ГГц и выше. Технология производства – 0,13 мкм, SOI. Срок выхода – 2002 г.

SledgeHammer – серверный вариант ClawHammer. Обеспечена поддержка до восьми процессоров. Технология производства – 0,13 мкм, SOI. Предполагаемый срок выхода – 2002 г.

3.3. Процессоры Cyrix

Cyrix — американская компания, производившая микропроцессоры. Процессоры её производства имели отличительные от остальных производителей процессоров для архитектуры x86 особенности, но, в целом, не получили такого большого распространения как Intel или AMD (Рис. 3.3)

Рис. 3.3. Процессоры Cyrix

6x86 – наименование процессоров Cyrix. Для оценки производительности относительно процессора Pentium использовался P-Rating, показывающий частоту, на которой пришлось бы работать процессору Pentium для достижения такой же производительности. P-Rating 6x86 составлял от 120 до 200 МГц. Кэш первого уровня – 16 Кбайт. Частота шины процессора – от 50 до 75 МГц. Разъем – Socket 5 и Socket 7.

M1 – то же, что и 6x86.

MediaGX – ответвление в семействе процессоров Cyrix. Первый процессор, сделанный по идеологии PC-on-a-chip. К ядру 5х86 были добавлены контроллеры памяти и PCI, в чип интегрирован видеоускоритель с кадровым буфером в основной памяти PC. В последних моделях используется ядро 6x86. В чипе-компаньоне реализован мост PCI-ISA и интегрирован звук. PR-рейтинг от 180 до 233 МГц, кэш-память L1 – 16 Кбайт. Производился по техпроцессу 0,5 мкм.

6x86MX – переработанный с целью достижения большей производительности вариант 6x86. Кэш-память L1 – до 64 Кбайт. В состав архитектуры ядра был добавлен блок MMX. Появилась поддержка раздельного питания. Частота шины процессора – от 60 до 75 МГц. PR-рейтинг – от 166 до 266 МГц. Процессоры 6х86MX делала и компания IBM. Их изделия 6х86MX имели рейтинг от 166 до 333 и были рассчитаны на частоту шину 66, 75, 83 МГц. Позднее, по маркетинговым соображениям, Cyrix переименовал свои процессоры в MII, а IBM до конца сотрудничества продавала их под маркой 6x86MX.

MII – последний процессор Cyrix, начал производиться в марте 1998 года. Кэш-память L1 – 64 Кбайт (единый), L2, как обычно для Socket 7, находится на материнской плате и имеет объем от 512 Кбайт до 2 Мбайт, работая на частоте системной шины. Поддерживаемые наборы инструкций – MMX. Использует PR-рейтинг. При производстве применялся техпроцесс 0,25 мкм.

Cayenne – кодовое наименование ядра, используемого в Gobi и MediaPC.

Gobi (MII+) – процессор, рассчитанный на платформу Socket 370. Поддерживаемые наборы инструкций – MMX, 3D Now!. Значительно переработан блок операций с числами с плавающей запятой. Кэш-память L1 – 64 Кбайт, кэш-память L2 – 256 Кбайт на чипе, работающие на полной частоте ядра процессора.

3.4.Риск процессоры

RISC-архитектура предполагает реализацию в ЭВМ сокращенного набора простейших, но часто употребляемых команд. Это позволяет упростить аппаратные средства процессора и получить возможность повысить его быстродействие. При использовании RISC-архитектуры выбор набора команд и структуры процессора направлены на то, чтобы команды набора выполнялись за один машинный цикл процессора. Выполнение более сложных, но редко встречаемых операций обеспечивают подпрограммы (Рис. 5).

Рис. 5.Риск процессор

mP6 – первые процессоры компании Rise. Предназначены для ноутбуков, использующих Socket 7. Отличаются очень малым тепловыделением. Кэш-память L1 – 16 Кбайт (по 8 Кбайт для данных и инструкций), L2 – от 512 Кбайт до 2 Мбайт, расположена на материнской плате, работает на частоте шины процессора. Поддерживается дополнительный набор инструкций MMX. При оценке производительности своих процессоров Rise, как и Cyrix, использует PR-рейтинг, составляющий от 166 до 366 МГц.

mP6 II – процессоры, отличающиеся от своих предшественников mP6 тем, что в чип интегрирована кэш-память L2 объемом 256 Кбайт. Была обещана поддержка SSE, производительность от PR-200 и выше. Однако в августе 1999 было объявлено об отмене планов по выходу процессора из-за значительного удорожания после добавления L2 в чип.

Tiger – mP6 II для платформы Socket 370. Кэш-память L1 – 16 Кбайт, L2 – 256 Кбайт, работающая на тактовой частоте ядра процессора. Выпуск отменен.

Глава 4.Песпективы развития процессоров. Процессоры для виртуальной реальности

В настоящее время значительное внимание ведущих исследовательских центров уделяется внедрению систем виртуальной и дополненной реальности (VR/AR) в образовательную деятельность. Данная тематика одинаково актуальна как для традиционных ВУЗовских процессов, так и для функционирования учебных центров в интересах силовых структур.

Применение средств виртуальной реальности в военно-учебной сфере нашло наибольшее развитие в США, Великобритании и Израиле.

Самый большой из известных учебных центров с применением технологий виртуальной реальности создан в Великобритании. CATT/Combined Arms Tactical Trainer («Тактический тренажёр боя с использованием различных видов вооружений») представляет собой полноценный тренажёр, способный заменить реальные тренировочные лагеря в условиях, максимально приближённых к боевым.

Наиболее близким к описываемому является российский проект, стартовавший на факультете информационных систем и технологий университета «Университет» в 2013 году. Проект был успешно представлен в декабре 2013 года в рамках конкурса «Премия инноваций Сколково при поддержке Cisco I-Prize». В 2014 году проект был остановлен из-за распада рабочей группы проекта. Инфраструктурно проект был основан на использовании программно-аппаратных средств московского ЦОД компании «Ай-Теко», предоставляемых в режимах PaaS и SaaS.

Идея описываемого проекта VAS4ME (Virtual Adaptive System For Mobile Education) заключается в создании распределённой обучающей среды, способной в сверхшироких диапазонах настраиваться под предпочтения конкретного пользователя (обучающегося) и под цели/задачи обучения. Настройка и обучение могут производиться как в индивидуальном, так и в групповом режиме обучения в составе группы или подразделения.

Основные составные части системы:

1) модули хранения:

1.1) хранилище образовательного контента;

1.2) хранилище тестовых наборов адаптивной настройки;

1.3) хранилище знаний о процессе обучения;

1.4) хранилище знаний по адаптации контента;

1.5) хранилище знаний по программно-аппаратным средствам, имеющим подтверждённую работоспособность с рассматриваемой системой;

2) модули воспроизведения:

2.1) система статобработки результатов тестирования и информации о ходе образовательного процесса;

2.2) система воспроизведения контента;

2.3) система формирования образов виртуальных [синтезированных] участников процесса;

2.4) система формирования виртуального [синтезированного] окружения обучающегося;

3) модули принятия решения:

3.1) система оценки личности обучающегося;

3.2) система оценки целей и задач обучения;

4) модули развития системы и самообучения:

4.3) система оценки эффективности процесса обучения;

4.4) система формирования рекомендаций по улучшениям;

4.4) система самообучения VAS4ME;

5) модули управления:

5.1) система управления тестированием;

5.2) система управления адаптацией процесса обучения;

5.3) система управления процессом обучения;

6) интерфейсные модули:

6.1) интерфейсы с внешними сервисами;

6.2) интерфейсы с приборами и датчиками контроля состояния обучающегося;

7) модули контроля состояния обучающегося:

7.1) распознавание позы;

7.2) распознавание мимики;

7.3) оценка физиологических параметров (давление, сердцебиение и т.п.)

и т.д..

8) модули контроля действий прошедшего обучение;

9) модули информационной безопасности;

10) модули дальнейшего расширения.

Построение системы осуществляется по принципам распределенных информационных систем. Основные модули системы размещены в специализированных центрах обработки данных (ЦОД), оснащенных соответствующими средствами коммуникации.

Периферийные устройства (аппаратная часть средств виртуальной реальности и контроля состояния обучаемого) выбираются, исходя из существующего уровня технологического развития из числа представленных на рынке.

Состав технических систем VAS4ME зависит от стадии реализации проекта. Начальными принципами построения системы являются открытость, расширяемость и масштабируемость.

На стадии полнофункциональной работы VAS4ME имеет в распределённом варианте (перечень не является полным):

1) ИТ-системы:

1.1) вычислительные платформы (серверы баз данных, приложений, файловые и т.п.);

1.2) системы хранения данных;

1.3) системы резервного копирования данных;

1.4) средства информационной безопасности;

1.5) телекоммуникационные средства (LAN, SAN, WAN);

1.6) структурированные кабельные системы (СКС);

1.7) компьютерное периферийное оборудование (принтеры, сканеры и т.п.);

2) системы жизнеобеспечения:

2.1) система автоматизации и диспетчеризации объекта(ов);

2.2) система энергоснабжения;

2.3) система вентиляции и кондиционирования;

2.4) система видеонаблюдения;

2.5) система контроля и управления доступом;

2.6) система противопожарной автоматики и пожаротушения;

2.7) система антитеррористической защиты;

2.8) система радиофикации и оповещения;

3) системы виртуальной и дополненной реальности:

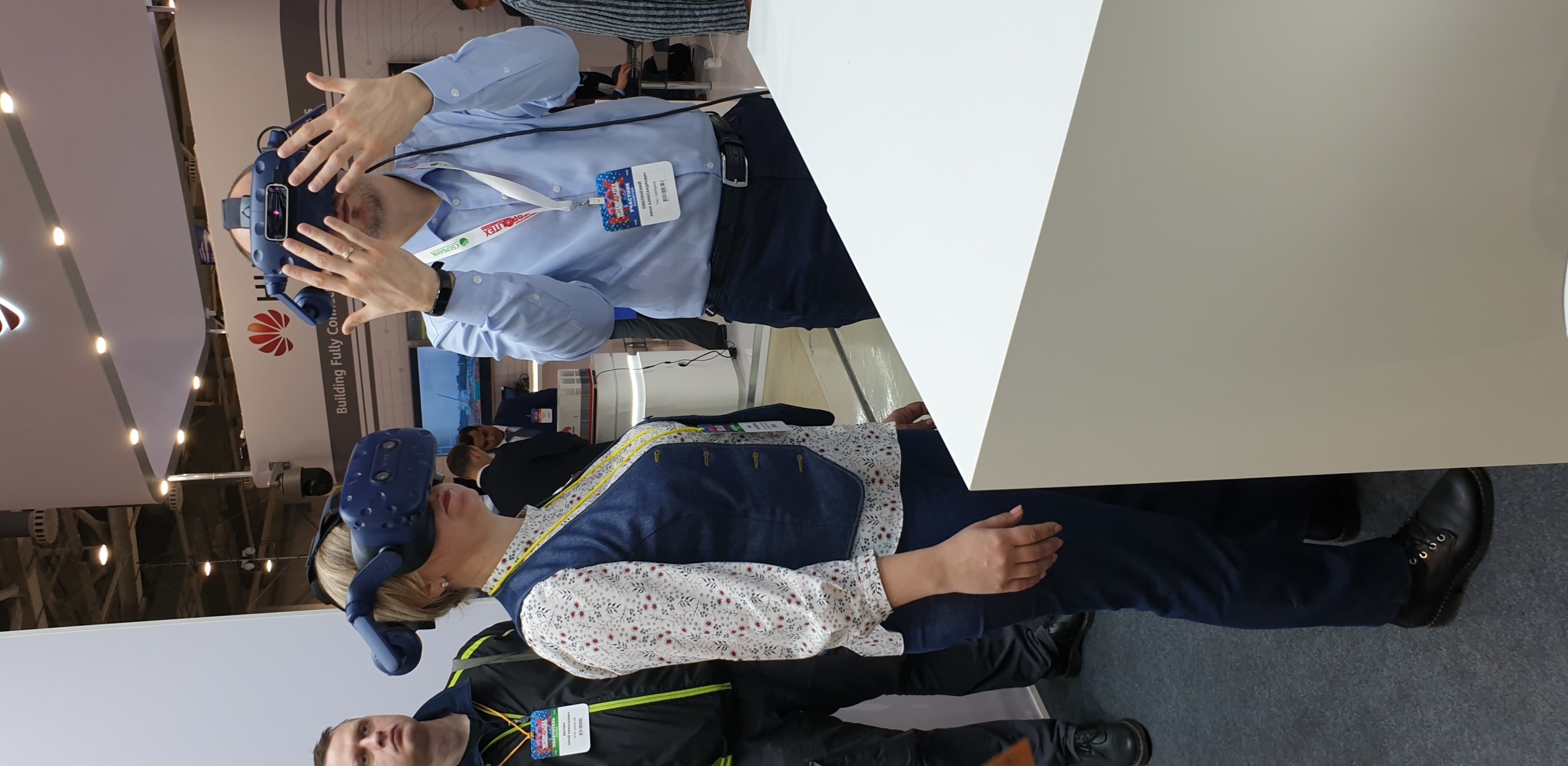

3.1) очки и шлемы виртуальной реальности (фото 1);

3.2) перчатки и костюмы виртуальной реальности;

3.3) дорожки виртуальной реальности;

3.4) специализированные и индивидуальные тренажёры;

4) биометрические системы (оценка позы, контроль частоты дыхания, сердечного ритма, кожная проводимости и др.).

Архитектурно система состоит из распределённого ядра и абонентских систем различных типов, например:

1) индивидуальное учебное место;

2) учебный класс;

3) учебный центр и т.п.

Эталонный образовательный контент находится в составе распределённого ядра системы. Отдельные копии контента могут находиться в составе абонентских систем.

Абонентские системы могут иметь произвольное местоположение:

- орбитальное (для случая пилотируемых КА);

- воздушное (самолёты, вертолёты, дирижабли и т.п.);

- морское и речное;

- наземное;

- как вариант, подземное и подводное.

Распределение образовательного контента для абонентских систем может выполняться в on-line или off-line режиме. Для off-line режима доступны варианты использования телекоммуникационных систем, либо съёмных носителей информации.

В качестве транспортной среды доставки контента и телеметрических данных могут быть использованы практически любые доступные средства и системы связи (военные и коммерческие):

1) спутниковые:

- радио;

- оптические;

2) мобильные;

3) фиксированные:

- кабельные (электрические);

- оптоволоконные;

- оптические атмосферные;

- радио;

- акустические.

По технологии построения абонентские системы могут быть локальными, локально-централизованными и распределёнными.

Для локального варианта функции обработки, визуализации и обратной связи сосредоточены в одном устройстве. Самым простым вариантом подобного построения является использование индивидуальных смартфонов, планшетов и иных персональных программно-аппаратных средств.

Локально-централизованный вариант предполагает работу в стиле «мейнфрейма», когда вся информационная обработка осуществляется центральным блоком, обслуживающим некоторое количество терминальных систем.

Распределённая технология построения предусматривает распределение функций обработки между несколькими устройствами, входящими в состав абонентской системы.

В состав абонентских систем предполагается введение различных средств индивидуальных и групповых средств виртуальной реальности (Рис. 6).

Рис. 6. Групповая работа с очками виртуальной реальности на выставке «Интерполитех-2019»

Для оценки состояния обучающегося в ряде случаев могут быть использованы специализированные контактные и бесконтактные средства контроля физиологических параметров.

Заключение

В работе проведен анализ процессоров персонального компьютера. Исследованы назначение и структура процессора персонального компьютера. Проанализированы функции процессора персонального компьютера. Рассмотрены процессоры для виртуальной реальности.

Проведена классификация процессоров.

Таким образом, цель и задачи, поставленные в курсовой работе выполнены.

Результаты исследований в дальнейшем будут использоваться для написания дипломного проекта.

Список литературы

- Александров Е.К., и др. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ. Учебное пособие для вузов / Санкт-Петербург, 2016.

- Андреев А.Е., Егунов В.А., Жариков Д.Н., Конченков В.И. СПЕЦИАЛИЗИРОВАННЫЕ ПРОЦЕССОРЫ. Учеб.-метод. пособие / Волгоград, 2017.

- Воробьева А.П., Галкина Ю.А. СОВРЕМЕННЫЕ КОМПЬЮТЕРНЫЕ ТЕХНОЛОГИИ. Лабораторный практикум для студентов всех направлений / Новосибирск, 2016. Том Часть 1

- Гриценко Ю.Б. ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ, СЕТИ И ТЕЛЕКОММУНИКАЦИИ -Томск, 2015.

- Гуров В.В. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ. Учебник / Москва, 2016. Сер. Бакалавриат

- Евдокимова С.А., Цикоза Л.П. ИНФОРМАТИКА. Практикум / Воронеж, 2018.

- Журавлева Т.Ю. ИНФОРМАЦИОННЫЕ ТЕХНОЛОГИИ. Учебное пособие / Саратов, 2018.

- Калачев А.В. МНОГОЯДЕРНЫЕ ПРОЦЕССОРЫ - Москва, 2016.

- Лебедев В.И. ИНФОРМАТИКА. Курс лекций на английском языку / Ставрополь, 2015.

- Некрасов К.А., Поташников С.И., Боярченков А.С., Купряжкин А.Я. ПАРАЛЛЕЛЬНЫЕ ВЫЧИСЛЕНИЯ ОБЩЕГО НАЗНАЧЕНИЯ НА ГРАФИЧЕСКИХ ПРОЦЕССОРАХ . Учебное пособие / Министерство образования и науки Российской Федерации, Уральский федеральный университет. Екатеринбург, 2016.

- Николаев Е.И. ПАРАЛЛЕЛЬНЫЕ ВЫЧИСЛЕНИЯ. Учебное пособие / Ставрополь, 2016.

- Пирогов В.Ю. 64-БИТОВЫЕ ПРОЦЕССОРЫ: ОСОБЕННОСТИ ПРОГРАММИРОВАНИЯ ДЛЯ ПЛАТФОРМ WINDOWS И UNIX - Шадринский государственный педагогический институт. Шадринск, 2016.

- Попов Е.В. ОБЗОР РАЗВИТИЯ МИКРОПРОЦЕССОРОВ. В сборнике: Студенческая наука Сборник научных трудов. Теоретические и практические результаты исследований бакалавров, магистров и аспирантов. Москва, 2018. С. 151-155.

- Рудометов Е. А. «Современное железо: настольные, мобильные и встраиваемые компьютеры» СПб.: БХВ-Петербург, 2010. — 464 с.: ил.

- Рыбальченко М.В. ОРГАНИЗАЦИЯ ЭВМ И ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА. Учебное пособие / Южный федеральный университет. Ростов-на-Дону-Таганрог, 2017.

- Стариков В.М., Воронина Н.И. ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ. Учебное пособие для студентов дневного, заочного обучения и ФДПО / Министерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования «Ярославский государственный технический университет». Ярославль, 2015.

- Степина В.В.АРХИТЕКТУРА ЭВМ И ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ - Москва, 2017.

- Филимонова Е.В. ИНФОРМАЦИОННЫЕ ТЕХНОЛОГИИ В ПРОФЕССИОНАЛЬНОЙ ДЕЯТЕЛЬНОСТИ. Учебник / Москва, 2017. Сер. Среднее профессиональное образование

- Шаршунов В.А., Шаршунов Д.В., Титов В.Л. ИНФОРМАТИКА И ИНФОРМАЦИОННЫЕ ТЕХНОЛОГИИ. Пособие / Минск, 2017.

- Юдина Н.Ю. ВЫЧИСЛИТЕЛЬНЫЕ МАШИНЫ, СИСТЕМЫ И СЕТИ -Воронеж, 2015.

Электронные ресурсы

- Интеллект. URL: https://intellect.icu/tema-17-risk-protsessory-lektsiya-24-4652 (дата просмотра 30.01.2020)

- Источник для технологий покупки. URL: https://www.techradar.com/news/best-processors (дата просмотра 30.01.2020)

- Планета информатики URL: https://inf1.info/processor (дата просмотра 30.01.2020)

- Система классификации и именования процессоров. www.ixbt.com/cpu/codenames.html (дата просмотра 30.01.2020)

- Функции операционных систем персональных компьютеров

- Система защиты информации в зарубежных странах .

- Проектирование реализации операций бизнес-процесса «Продажи»

- Лицензирование отдельных видов предпринимательской деятельности

- Виды договоров и их особенности

- Назначение и структура системы защиты информации коммерческого предприятия (Сущность защиты информации и важность информации в деятельности предприятия)

- Факторы, влияющие на свойства сохраняемости группы однородных продовольственных товаров

- Эффективность судебной власти в России

- Особенности работы с персоналом, владеющим конфиденциальной информацией

- Проектирование реализации операций бизнес-процесса "Продажи"

- НАБОР, ОТБОР ПЕРСОНАЛА

- Языки гипертекстовой разметки