Процессор персонального компьютера. Назначение, функции, классификация процессора (Архитектура микропроцессора)

Содержание:

Введение

Актуальность темы заключается в том, что центральный процессор является основным устройством, осуществляющим обработку информации в структуре ЭВМ. Увеличение производительности микропроцессора повышает производительность всей вычислительной системы, что позволяет с каждым днем решать все более сложные задачи, например как увеличивать объем обрабатываемых данных, так и усложнять сам анализ в рамках концепции «Больших данных». Кроме производительности, к процессорам предъявляется еще ряд требований, связанных непосредственно с областью применения вычислительных устройств. К ним относятся, например, энергопотребление, тепловыделение, технологичность производства. О первых двух характеристиках речь обычно заходит при применении ЭВМ в мобильных устройствах и встраиваемых системах (особенно актуальными данные параметры стали в связи с развитием концепции «интернета вещей»). Сложность конструкции процессора повышает его себестоимость, а также ограничивает в выборе фабрики, способной освоить его производство.

Архитектура процессора напрямую обуславливает его инженерно-техническую реализацию, определяя вышеуказанные характеристики. С момента появления первого коммерчески успешного процессора Intel 4004, выпущенного 15 ноября 1971 года, и по сей день идет непрерывное совершенствование данных устройств, следствием чего является появление новых решений в области архитектуры.

Объектом данного исследования является архитектура микропроцессоров, ее влияние на основные характеристики данных устройств.

Предметом данного исследования являются процессоры RISC- и CISC-архитектуры.

Целью данного исследования является определение основных различий данных архитектур, сравнительная оценка их преимуществ и недостатков.

Задачами данного исследования являются:

-

- Исследование классификации микропроцессоров.

- Исследования общего устройства микропроцессоров.

- Исследование основных характеристик микропроцессоров.

- Исследование системы команд микропроцессоров

- Исследование режимов адресации микропроцессоров

- Исследование особенностей микропроцессоров CISC-архитектуры.

- Исследование особенностей микропроцессоров RISC-архитектуры.

Тема архитектуры микропроцессоров, ее совершенствования, широко представлена в специализированной литературе, что связано с востребованностью данных устройств на данном этапе научно-технического развития, длительный период существования рассматриваемой тематики, а также коммерческой успешностью фирм-производителей. Учитывая высокие темпы развития цифровых технологий, особую актуальность при рассмотрении данного вопроса имеют периодические специализированные издания.

Глава 1. Архитектура микропроцессора

1.1 Классификация микропроцессоров.

Центральный процессор (ЦП; также центра́льное проце́ссорное устро́йство — ЦПУ; англ. central processing unit,CPU, дословно — центральное обрабатывающее устройство) — электронный блок, либо интегральная схема (микропроцессор), исполняющая машинные инструкции (код программ), главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда называют микропроцессором или просто процессором. [10]

Основными критериями, на основе которых можно классифицировать микропроцессоры являются:

- Система команд микропроцессора. На основе данного критерия выделяют следующие основные архитектуры:

1. CISC-архитектура (Complex Instruction Set Computer) – компьютер с полным набором команд.

2. RISC-архитектура (Reduced Instruction Set Computer) – компьютер с сокращенным набором команд.

3. VLIW-архитектура (Very Long Instruction Word) – очень длинное командное слово.

- По разрядности микропроцессора: 8-разрядные, 16-разрядные, 32-разрядные, 64-разрядные.

- По назначению:

1. Микропроцессоры для встраиваемых систем, носимой электроники и «интернета вещей».

2. Микропроцессоры для мобильных устройств.

3. Микропроцессоры для настольных персональных компьютеров и рабочих станций.

4. Микропроцессоры для серверов и суперкомпьютеров.

- По компании-разработчику: Intel, AMD, ARM, Qualcomm, MediaTek, Samsung, и т.д.. [4]

1.2 Устройство микропроцессора.

В общем случае в устройстве процессора можно выделить три функциональных блока: операционный блок, блок управления и интерфейсный блок.

Функциональный блок состоит из следующих элементов:

- Арифметическое логическое устройство (АЛУ). К задачам АЛУ относится реализация простейших арифметических и логических функций. Более сложные операции, для которых отсутствует аппаратная реализация, выполняются программным способом с использованием регистров общего назначения для хранения промежуточных данных.

- Блок управления определяет очередность поступления инструкций на выполнение. На него возложено выполнение следующих задач:

- Считывание и запоминание текущей инструкции.

- Определение адреса следующей команды.

- Реализация выполнения поступившей инструкции (Блок управления декодирует команду, разбивая ее на несколько микроинструкций, доступных для выполнения АЛУ, создавая таким образом микропрограмму).

- Управление поступлением информации с внешних устройств, и выводом на них по системной шине.

- Интерфейсный блок обеспечивает коммуникацию между процессором и системной шиной. Системная шина включает в себя шину управления, шину данных и шину адреса. [4]

1.3 Характеристики микропроцессора.

К основным характеристикам микропроцессора относятся:

1) Тактовая частота процессора, которая определяет максимальное время выполнения переключения элементов в процессорном устройстве;

2) Разрядность: максимальное число одновременно обрабатываемых двоичных разрядов.

Разрядность микропроцессора принято обозначать как m/n/k/, что подразумевает:

m - разрядность внутренних регистров.

n - разрядность шины данных. Данный показатель определяет скорость передачи данных;

k - разрядность шины адреса, определяет размер адресного пространства. Например, для микропроцессора Intel 8088 верны следующие значения m/n/k: 16/8/20.[10]

3) Архитектура. Под архитектурой микропроцессора понимают систему команд и способы адресации, возможность одновременного выполнения инструкций, наличие дополнительных блоков в конструкции микропроцессора, принципы и режимы его работы. При этом принято выделять понятия микроархитектуры и макроархитектуры.

Микроархитектура микропроцессора - это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали.

Макроархитектура - это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора. [7]

1.4 Система команд

Под системой команд процессора принято понимать полный перечень команд, которые способен выполнить данные процессор. В свою очередь под архитектурой системы команд подразумевают те средства вычислительной машины, которые видны и доступны программисту. [1]

Время выполнения программы (Tвыч) определяется через число команд в программе (Nком), среднее количество тактов процессора, приходящихся на одну команду (CPI ), и длительность тактового периода tпр равенством вида Tвыч = Nком × CPI × tпр

Каждый из перечисленных параметров зависит от архитектуры системы команд. [6]

В общем виде архитектура системы команд определяется, исходя из следующих факторов:

- Вид данных и форма представления данных в ЭВМ.

- Область хранения данных, помимо основной памяти.

- Метод осуществления доступа к данным.

- Характер операций, выполняемых над данными.

- Количество операндов в команде.

- Способ определения адреса следующей команды.

- Способ кодирования команд.

Проектирование системы команд во многом определяет структуру ЭВМ. Оптимальную систему команд иногда принято определять как совокупность команд, которая обеспечивает проблемно-ориентированное применение таким образом, что избыточность аппаратных и аппаратно-программных средств на реализацию редко используемых команд оказывается минимальной. В различных программах частота применения тех или иных команд различна. Например, по данным фирмы Digital Equipment Corporation в программах для ЭВМ семейства PDP-11 чаще других применялась инструкция передачи MOV(B). Ее доля составляла около 32% от всех инструкций в распространенных программах. Систему команд микропроцессора следует формировать таким образом, чтобы на исполнение редко используемых команд затрачивалось минимальное количество ресурсов.

Проведя анализ программного обеспечения, и получив определенный набор статистических данных, можно спроектировать процессор с эффективной системой команд. Одним из направлений оптимизации архитектуры системы команд является разработка инструкций длиной в одно слово и их кодирования соответствующим образом, позволяющим оптимально применять разряды коротких инструкций, что обеспечивает сокращение времени выполнения программы и ее размер. [7]

Другим направлением оптимизации является использование микроинструкций. При таком подходе отдельные биты используются для кодирования нескольких элементарных операций, которые группируются и выполняются в одном командном цикле. Данные элементарные операции не выполняют обращения к памяти, а очередность их выполнения обеспечивается аппаратной логикой.

При этом подходе снижение количества времени, требуемого для выполнения программы, и ее размера достигается за счет повышения сложности блока управления. [8]

Одной из основных характеристик инструкций является их формат. Формат команды определяет ее составляющие элементы, которые интерпретируются соответствующим образом при исполнении.

К данным элементам относятся: код операции, определяющий выполняемое действие; адрес ячейки памяти, регистра процессора, внешнего устройства; режим адресации; операнд при использовании непосредственной адресации; код анализируемых признаков для команд условного перехода.

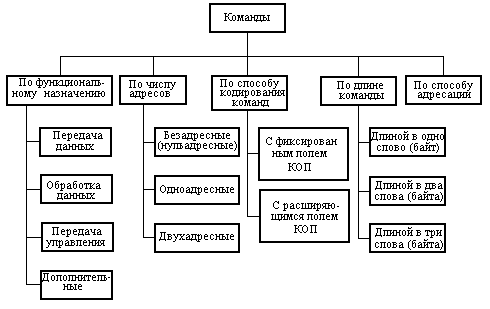

Классификация команд по основным признакам представлена на рис. 1

Одним из основных структурных элементов формата любой инструкции является код операции (КОП), который непосредственно определяет действие, которой должно быть исполнено. Аппаратная реализация команд позволяет снижать размер программы и сокращать время ее выполнения, что теоретически должно обеспечивать преимущество процессора. Однако при проектировании (или выборе) системы команд следует учитывать непосредственно комплекс инструкций, предназначенный для работы с требуемым типом данных, а не только общее количество команд, а также доступные режимы адресации.

Число бит, отводимое под КОП зависит от количества реализуемых команд.

Рис. 1 Классификация команд.

При использовании фиксированного числа бит под КОП для кодирования всех m команд необходимо в поле КОП выделить двоичных разрядов. Однако, учитывая ограниченную длину слова мини- и микроЭВМ, различное функциональное назначение команд, источники и приемники результатов операций, а также то, что не все команды содержат адресную часть для обращения к памяти и периферийным устройствам, в малых ЭВМ для кодирования команд широко используется принцип кодирования с переменным числом бит под поле КОП для различных групп команд.

Инструкции можно разделить на однооперандные и двухоперандные, соответственно по количеству операндов, задействованных при исполнении инструкции. Как правило, при использовании двух операндов инструкцией модифицируется лишь один из них. Поскольку данные извлекаются только из одной ячейки, то такая ячейка носит название источника. Ячейка, чье содержимое подвергается модификации определяется как приемник.

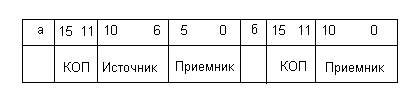

В данном примере указан формат двухадресной (двухоперандной) команды ЭВМ СМ (семейство ЭВМ, разработанных странами СЭВ в конце 70-х — начале 80-х годов; отдельные представители совместимы по набору команд с DEC PDP 11).

Таблица 1. Примеры кодирования двухадресных команд в процессорах СМ

Таблица 1. Примеры кодирования двухадресных команд в процессорах СМ

|

КОП |

Мнемоника команды |

Комментарий |

|

0001 |

MOV |

Передача данных |

|

0000 |

- |

Кодирование группы |

Таблица 2. Двухоперандные операции

Четырехбитный КОП (биты 15-12) формирует ряд двухоперандных операций, представленных в таблице 2. Биты (11-6) и (5-0) в данном формате представляют адреса источника и приемника данных. Комбинации 0000 и 1000 поля КОП представляют группы одноадресных команд. КОП 1 (биты 15-12), представленный кодами 0000 и 1000, обозначает группу одноадресных инструкций, а КОП 2 (биты 11-6) обозначает конкретную инструкцию команд этой группы. Таким образом, однооперандные инструкции кодируются 10-битным КОП (биты 15-6).

Сложные команды порой задействуют до четырех операндов. Например, операция сложения может указывать адреса слагаемых, адрес результата и адрес следующей команды. Если при этом адрес задается 16 битами, то четырехоперандная инструкция потребует 8 байт памяти (без учета кода инструкции). Как следствие, ЭВМ, основанная на подобной системе команд будет обладать невысоким быстродействием и большим размером программ. В связи с этим в большинстве применяемых процессоров любая инструкция задействует не более двух операндов.

Это обеспечивается с применением следующих методов:

1. Адрес следующей команды непосредственно указывается только при использовании команд переходов; в остальных случаях очередная инструкция извлекается из ячейки памяти, следующей за исполненной инструкцией.

2. Применение ячейки памяти, из которой извлекался один из операндов, для записи результативного значения.

Возможные варианты обращения к операндам обеспечивается различными режимами адресации. При использовании нескольких режимов адресации в формат команды включены биты, предписывающие режим адресации для операнда. К примеру, для использование восьми режимов адресации требуется три бита.

В большинстве форматов команд в первые биты проводится запись кода операции, но в остальном форматы команд различных процессоров значительно дифференцированы. Остальные биты используются для указания операндов или адреса их нахождения, поэтому они применяются для кодирования комбинаций режимов, адресов регистров, адресов памяти, относительных адресов и непосредственных операндов. Как правило, длина команды может составлять от 1 до 3 и даже 6 байт.

Формат команд во многом определяет возможности процессора. [3]

1.5 Режимы адресации.

Для обеспечения организованной работы различных компонентов ЭВМ каждая ячейка памяти (как внешней, так и внутренней), регистры микропроцессора и регистры устройств ввода/вывода должны иметь свой идентификатор. Поэтому каждой из ячеек памяти присваивается ее адрес., то есть уникальная комбинация бит. От числа задействованных бит зависит количество идентифицируемых ячеек. Как правило, компьютер имеет различные адресные пространства памяти и регистров микропроцессора. Стоит учитывать, что в памяти хранятся как данные, так и инструкции. Вследствие этого, для оптимальной реализации программ реализовано множество способов доступа к памяти — режимов адресации.

Режим адресации памяти — это процедура или схема преобразования адресной информации об операнде в его исполнительный адрес.

Различные режимы адресации делятся на:

- Прямой режим, при котором исполнительный адрес извлекается непосредственно из инструкции, или высчитывается с применением параметра, представленного в инструкции, и значения какого-либо регистра.

- Косвенные режим, при котором в инструкции заключено значение косвенного адреса, т.е. ячейки памяти, содержащей указание на исполнительный адрес.

В каждом компьютере реализовано только несколько режимов адресации, применение которых определено архитектурой микропроцессора. [1]

Глава 2. Архитектура системы команд: CISC и RISC

2.1 Особенности микропроцессоров CISC-архитектуры.

Исторически, первой активной совершенствующейся архитектурой системы команд процессора стала CISC-архитектура (Complex Instruction Computer Set – компьютер с полным набором команд).

Это обусловлено рядом факторов, к которым, в частности, относились следующие:

- Значительная часть программного обеспечения создавалась с применением языка программирования низкого уровня – ассемблера, что объясняется невысоким уровнем производительности ранних процессоров.

- Использование сложных инструкций позволяло сократить размеры написанной на ассемблере программы. В свою очередь это уменьшало затраченное на исполнение программы время, а также позволяло экономить такой дорогостоящий ресурс, как оперативная память. [2]

- Более активное использование языков высокого уровня с целью облегчения процесса программирования, оптимизации решения специализированных задач, создало проблему, определенную как «семантический разрыв». Семантический разрыв - это мера различия принципов, лежащих в основе языков программирования высокого уровня, и тех принципов, которые определяют архитектуру ЭВМ. Усложнение системы команд процессора позволяло приблизить ее к языкам высокого уровня, сокращая этот разрыв. [6]

Основоположником CISC-архитектуры принято считать компанию IBM и ее семейство ЭВМ IBM 360. В дальнейшем CISC-архитектура была реализована во множестве процессоров, таких, как Intel 80x86, Motorola 68k, Zilog Z80xxx.

Для процессоров CISC-архитектуры характерны следующие общие черты:

- наличие в процессоре сравнительно малого количества регистров общего назначения;

- большое количество инструкций, часть из которых аппаратно реализуют функции сложных операторов языков высокого уровня;

- множество способов адресации операндов

- множество форматов тнструкций различной разрядности;

- наличие команд, совмещающих обработку с обращением к памяти. [5]

Одним из популярных процессоров данной архитектуры являлся Motorola 68000, широко применявшийся в ПК различных семейств, таких как Commodore Amiga, Atari ST, Apple Macintosh, Sinclair QL.

Регистровая архитектура M68000 — это образец микропроцессора с полным набором команд. Архитектура системы команд включает в себя две группы 32-битовых регистров общего назначения, имеющих специализацию (восемь регистров для данных, семь регистров для адресации), два 32-битовых регистра указателей стека (один — пользовательского, второй — суперпользовательского режимов) и 32-битный счетчик команд PC. Система команд 68000 по своей сложности близка к языкам высокого уровня.

Основная система команд включается в себя 56 инструкций, и 14 способов адресации, что увеличивает количество доступных программисту вариантов исполнения команд.

Инструкции Motorola 68k можно разделить на следующие группы:

- Операции с памятью (Load&store — Move.B, Move.W, Move.L);

- Арифметика (Add, Sub, Mul, Div);

- Побитное смещение (влево и вправо, логическое и арифметическое);

- Циклические битовые сдвиги (ROR, ROL, ROXL, ROXR);

- Логические операции (And, Or, Not, EOr);

- Конверсия типов (байт в слово и наоборот);

- Условное и безусловное ветвление (Bra, BCS, BEq, BNE, BHI, BLO, BMI, BPL, etc.);

- Вызов подпрограмм и возврат из них (BSR, RTS);

- Управление стеком (push, pop);

- Вызов и обработка прерываний;

- Обработка ошибок и исключений. [12]

Несмотря на свои высокие характеристики процессоры CISC-архитектуры обладают рядом недостатков, ведущими из которых считаются:

- Сложность в разработке и производстве процессоров, что обуславливает их сравнительно высокую стоимость.

- Трудности формирования параллельности и конвейеризации вычислений.

К тому же, ряд исследований, проведенных, в частности компанией IBM показал избыточность сложности архитектуры системы команд CISC-процессоров – программисты, пишущие программы на ассемблере, так же, как и компиляторы, не использовали значительную часть команд (доля дополнительных команд, эквивалентных операторам языкам высокого уровня, в общем объеме программ не превышает 10–20%, а для некоторых, наиболее сложных команд, даже 0,2%).

В технологии производства CISC-процессоров так же появился ряд проблем. В частности, из-за высокой сложности процессоров стало трудно наращивать их тактовую частоту. [6]

В результате для дальнейшего роста производительности потребовалось применение новых технологий архитектуры системы команд. Одной из таких технологий, ставшей коммерчески успешной, является RISC-архитектура.

2.2 Особенности микропроцессоров RISC-архитектуры.

Термин RISC впервые был использован Д. Паттерсоном и Д. Дитцелем в 1980 году. Данная аббревиатура расшифровывается как Reduced Instruction Set Computer - компьютер с сокращённой системой команд.

Основными принципами, лежащими в основе первых RISC-процессоров являются:

-

- Малое количество инструкций (в прототипах процессоров MIPS и SPARC отсутствовали инструкции умножения и деления)

- Малое количество способов адресации памяти. Обращение к памяти выполняется лишь с помощью специальных команд чтения и записи. В классическом варианте RISC из инструкций, обращающихся к оперативной памяти, оставлены только две (Load - загрузить данные в регистр и Store - сохранить данные из регистра; так называемая Load/Store-архитектура).

- Малое количество форматов команд и способов указания адресов операндов. [2]

Яркой особенностью RISC-процессоров является большое количество регистров общего назначения (GPR) – как правило, их не менее шестнадцати. Все эти регистры полностью равнозначны, что позволяет компилятору свободно использовать их, сохраняя именно в них большую часть промежуточных данных, вместо обращению к стеку или более медленной оперативной памяти. [7]

В противоположность RISC-процессорам в классическом CISC-процессоре семейства 80x86 IA-32 всего восемь регистров общего назначения, при этом для каждого из них предусмотрена та, или иная специализация (для примера: в ESP хранится указатель на стек) затрудняющая его использование.

Данные действия позволили существенно упростить аппаратную реализацию процессора и повысить его быстродействие. По сути, целью разработки RISC-архитектуры являлось уменьшение Tвыч за счет сокращения CPI и tпр. Замена сложных инструкций последовательностью простых, но быстрых RISC-команд оказалась не менее эффективна, чем аппаратная реализация сложных команд в CISC-архитектуре. [6]

Считается, что первые элементы RISC-архитектуры появились в вычислительных машинах CDC 6600 и ЭВМ компании Cray Research разработки Сеймура Крея. Полноценное определение RISC-архитектуры, в современном её понимании, было сформировано на основе трех исследовательских проектов: процессора 801 компании IBM, процессора RISC университета Беркли и процессора MIPS Стенфордского университета.

Разработка экспериментального процессора компании IBM началась еще в конце 70-х годов, однако коммерческой реализации он не получил. В 1980 году Д. Паттерсон со своими коллегами из Беркли начали свой проект и изготовили два прототипа процессоров, которые получили названия RISC-I и RISC-II. К основным идеям этих машин относилось следующее:

- Отделение медленной памяти от высокоскоростных регистров

- Использование регистровых окон.

В 1981году Дж. Хеннесси со своими коллегами опубликовал описание процессора MIPS, основной особенностью разработки которой была эффективная реализация конвейерной обработки посредством планирования компилятором его загрузки. [11]

Самыми коммерчески востребованными оказались RISC-процессоры семейства Advanced RISC Machine, исходно разработанные компанией Acorn Computers и примененные в персональных компьютерах ее разработки (Acorn Archimed, RISC PC).

Для всех перечисленных процессоров характерны следующие общие черты:

- Отделение команд обработки от команд работы с памятью

- Акцент на эффективной конвейерной обработке. [9]

2.3 Конвейеризация вычислений.

Одна из особенностей конвейера, состоит в том, что производительность цепочки последовательных действий определяется не сложностью этой цепочки, а длительностью самой сложной операции. Применительно к процессорам принцип конвейера проявляется следующим образом: если разделить выполнение машинной инструкции на несколько этапов, то тактовая частота будет обратно пропорциональна максимальному времени выполнения самого медленного этапа. Если это время удастся сделать предельно малым (за счет разбития сложных действий на некоторое количество упрощенных), то удастся резко увеличить тактовую частоту, а значит, и производительность процессора.

Механизм исполнения практически любой инструкции можно разбить на пять независимых этапов:

- Изъятие инструкции из памяти (FETCH). Из памяти извлекается инструкция, которая подлежит выполнению.

- Декодирование инструкции (DECODE). Процессор переправляет запрос на требуемое исполнительное устройство.

- Подготовка исходных данных для выполнения инструкции.

- Собственно исполнение инструкции (EXECUTE).

- Сохранение полученных результатов.

Конвейеризация потенциально применима к любой процессорной архитектуре, независимо от набора команд и положенных в ее основу принципов. Подобные попытки предпринимались даже для такого процессора, как i8086, который уже содержал упрощенный "двухстадийный конвейер" - выборка новых инструкций (FETCH) и их исполнение осуществлялись в нем независимо друг от друга. Однако реализация этой технологии для CISC-процессоров оказалась крайне затруднительной: процесс декодирования слишком разнообразных по своей структуре и формату CISC-инструкций приводит к тому, что конвейер получается чересчур замысловатым, что значительно усложняет процессор. Подобных трудностей у RISC-архитектуры гораздо меньше в связи с их вышеперечисленными особенностями и изначальной оптимизацией для использования конвейеризации, так что коммерческие RISC-процессоры с данной технологией появились намного раньше, чем аналогичные x86.

Реализовать эффективный конвейер непросто. Среди основных проблем конвейеризации встречаются:

- Необходимость наличия блокировок конвейера. Поскольку время исполнения большинства инструкций может очень сильно варьироваться (для примера: умножение (и деление) чисел требуют (на стадии EXECUTE) нескольких тактов; сложение или побитовые операции - одного такта; а для операций Load и Store это время вообще не определено, поскольку данные инструкции подразумевают обращение как к различным уровням кэш-памяти, так и к оперативной памяти (и данный показатель может достигать сотен тактов)), то соответственно, возникает необходимость в механизме, который бы задерживал выборку и декодирование новых инструкций до тех пор, пока не будет завершено выполнение старых. Для решения этой проблемы были разработаны специальные функциональные блоки, которые располагаются в процессорах прямо перед исполнительными устройствами - блоки-диспетчеры (dispatcher). В данных блоках происходит накопление подготовленных к исполнению инструкций, а также осуществляется отслеживание выполнения ранее запущенных инструкций. В порядке освобождения исполнительных устройств диспетчеры отправляют на них новые инструкции. При возникновении ситуации, при которой исполнение конкретной инструкции занимает много тактов, внутренняя очередь диспетчера позволяет в большинстве случаев не останавливать подготавливающий все новые и новые инструкции конвейер. Поскольку новые инструкции удается декодировать не каждый такт, то возможной является и обратная ситуация: новых инструкций за такт не предоставлено, и диспетчер отправляет инструкции на выполнение из очереди во внутренней памяти. Таким образом, в процессоре функционально можно выделить две независимо работающие подсистемы: Front-end (блоки, занимающиеся декодированием инструкций и их подготовкой к исполнению) и Back-end (блоки, собственно исполняющие инструкции).

- Необходимость наличия системы сброса процессора. В связи с тем, что операции FETCH и EXECUTE всегда выделены в различные стадии конвейера, в тех случаях, когда в программном коде появляется разветвление (условный переход), возникает ситуация, при которой достоверно не известно, по которой из веток должно идти дальнейшее выполнение программы: инструкция, вычисляющая код условия, еще не выполнена. В результате процессор вынужден либо приостанавливать выборку новых инструкций до тех пор, пока не будет вычислен код условия (что занимает много времени, и значительно замедляет выполнение программы процессором), либо, продолжать выполнение программного кода в соответствии с указаниями блока предсказания переходов.

- Для эффективной работы конвейера требуется наличие специального планировщика (scheduler), предназначенного для решения конфликтов по данным. Суть его работы можно представить следующим образом: если в программе идет зависимая цепочка инструкций (при которой инструкция-2, следующая за инструкцией-1, использует для своих вычислений данные, только что вычисленные инструкцией-1), а время исполнения одной инструкции (от момента запуска на стадию EXECUTE и до этапа записи полученных результатов в регистры) занимает более одного такта, то процессор вынужден задержать выполнение инструкции-2 до тех пор, пока не будет полностью выполнена инструкция-1. Цепочки зависимых инструкций в программном коде возникают систематически проблема зависимости по данным сопровождает любую конвейерную архитектуру. С целью решения этих проблем в процессорах существуют декодеры, чьей функцией является выявление этих зависимостей, и планировщики, чьей задачей является выдерживание паузы между запуском главной инструкции и зависимой от нее.

Практическая реализация конвейера чрезвычайно сложна. Но рост производительности при использовании конвейеризации столь значителен, что техническое решение этих проблем является оправданным, несмотря на затраты на этапе разработки. [6]

Ярким примером эффективности этой технологии является выпуск в 1992 году корпорацией i486 - классического CISC-процессор архитектуры x86, но с пятистадийным конвейером. Применение конвейеризации позволило втрое повысить тактовую частоту в сравнении с 80386, а производительность в расчете на один такт – удвоилась. Если в процессорах серии i80386 многие инструкции выполнялись в течение нескольких тактов, то у процессора i80486 среднее количество тактов, затрачиваемых на инструкцию удалось снизить почти вдвое. Это стало возможным благодаря значительному усложнению архитектуры процессора.

Но к тому моменту коммерческие процессоры, выполненные в соответствии с RISC-архитектурой получили новые перспективные технологии — суперскалярность и внеочередное исполнение инструкций.

2.4 Технологии повышения производительности: суперскалярность и внеочередное выполнение инструкций.

Суперскалярность — архитектура вычислительного ядра, использующая несколько декодеров команд, которые могут загружать работой множество исполнительных блоков. Планирование исполнения потока команд является динамическим и осуществляется самим вычислительным ядром. [2]

Еще одной технологией, позволяющей повысить производительность RISC-процессоров является внеочередное исполнение инструкций - Out-of-Order processors. Суть ее заключается в том, что если выполнение какой-либо инструкции затягивается (например, при обращении к «медленной» оперативной памяти), то планировщик передает на исполнение другие инструкции, не зависящие от исполнения первой.

Следует заметить, что на сегодняшний день не существует ни одного суперскалярного или OoO CISC-процессора. Дело в том, что для нормальной реализации производительных диспетчеров и планировщиков требуется длительная и тщательная подготовка инструкций до такого простого состояния, чтобы эти, функционирующие на высоких частотах, функциональные блоки могли максимально быстро перенаправить поток инструкций на соответствующие исполнительные устройства. Поэтому любой исходный машинный код Front-end процессоров превращает перед исполнением в некое внутреннее, упрощенное состояние. Эта технология используется, в том числе, в современных процессорах семейства x86. То есть на данном этапе развития компьютерных технологий различия между RISC- и CISC-архитектурами почти. Так что можно сказать, что фактически все современные x86-процессоры полноценными RISC-процессорами - ведь исходный x86-код они в любом случае преобразуют в реальном времени во внутреннее RISC-подобное представление. [6]

Также следует отметить, что развитие архитектуры RISC во многом обязано прогрессу в области создания оптимизирующих компиляторов. Именно современная техника компиляции позволяет эффективно использовать преимущества большего регистрового файла, конвейерной организации и большей скорости выполнения команд. Современные компиляторы используют также преимущества другой вышеуказанной оптимизационной техники для повышения производительности, обычно применяемой в процессорах RISC: реализацию задержанных переходов и суперскалярной обработки, позволяющей в один и тот же момент времени выдавать на выполнение несколько команд. [1]

К процессорам с RISC-архитектурой, получившим наиболее широкое коммерческое применение относятся: ARM, SPARC, PowerPC, MIPS (последняя архитектура использовалась при создании отечественных процессоров семейства Baikal и китайских Godson).

Заключение

В данной работе рассмотрена архитектура команд микропроцессора. Приведена схема общего устройства микропроцессоров, их классификация. Раскрыты понятия архитектуры процессора, системы команд, оптимальной системы команд, режимов адресации, RISC-архитектуры, CISC-архитектуры, конвейеризации, суперскалярности, внеочередного выполнения команд.

Поставленные задачи выполнены в полном объеме. При выполнении данного исследования использовались как справочники, так и периодические издания.

Высокие требования, которые предъявляются к производительности вычислительных устройств при решении широкого круга задач в таких областях как экономический анализ, управление производством, трехмерное проектирование, моделирование биологических процессов, индустрия видеоигр и т. д., служат движущей силой, которая стимулирует дальнейшее совершенствование данных типов устройств. Одним из направлений оптимизации является совершенствование системы команд микропроцессоров. На сегодняшний день наиболее распространенными типами процессоров стали представители CISC- и RISC-архитектуры, при этом, в ходе «эволюции» микропроцессоров произошло слияние технологий, при котором образцы наиболее производительных CISC-процессоров являются RISC-устройствами на уровне непосредственного исполнения инструкций. Данное преобразование предоставляет возможность использовать преимущества RISC-архитектуры, позволяя при этом использовать наследие накопленного программного обеспечения для микропроцессоров семейства i80x86.

Кроме производительности, к микропроцессорам предъявляются такие требования, как энергопотребление, тепловыделение, технологичность производства. Данные характеристики находятся в зависимости от архитектуры системы команд. Исходя из данных требований, наиболее оптимальными для мобильных устройств, а также встраиваемых систем оказались процессоры RISC-архитектуры. К ним, в частности, относятся микропроцессоры семейства Baikal, разработанные Российской компанией Baikal Electronics, и использующие системы команд архитектур MIPS и ARM.

При этом следует отметить, что на сегодняшний день практически не осталось «классических» представителей RISC-архитектуры, которые бы массово использовались в персональных компьютерах и рабочих станциях. Однако данная ситуация может измениться в связи с развитием в КНР семейства микропроцессоров Godson (название архитектуры — Loongson) и выходом компании Qualcomm на рынок ноутбуков с процессорами семейства Snapdragon.

Дальнейшее развитие архитектуры системы команд является динамическим процессом, который ни на минуту не останавливается в научно-технических центрах компаний-разработчиков и лабораториях научно-исследовательских институтов.

Список литературы

1. Александров Е.К. Микропроцессорные системы [Электронный ресурс]: учебное пособие/ Александров Е.К., Грушвицкий Р.И., Куприянов М.С.— Электрон. текстовые данные.— СПб.: Политехника, 2012.— 935 c.

2. Гуров В.В. Архитектура микропроцессоров [Электронный ресурс]: учебное пособие/ Гуров В.В.— Электрон. текстовые данные.— М.: БИНОМ. Лаборатория знаний, Интернет-Университет Информационных Технологий (ИНТУИТ), 2010.— 272 c.

3. Ершова Н.Ю., Ивашенков О.Н., Курсков С.Ю. Микропроцессоры

Учебное пособие, электронная версия. - Петрозаводск: Петрозаводский государственный университет. - 110 стр.

4. Макарова Н., Волков В. Информатика. Учебное пособие для обучающихся по программе бакалавриата. Спб.: Питер, 2011 — 576 с.

5. Озеров С. Архитектура процессоров. CISC и RISC.// Компьютерра: журнал. - 2005.

6. Русанов В.В. Микропроцессорные устройства и системы [Электронный ресурс]: учебное пособие/ Русанов В.В., Шевелёв М.Ю.— Электрон. текстовые данные.— Томск: Томский государственный университет систем управления и радиоэлектроники, 2012.— 184 c.

7. Цилькер Б.Я. Организация ЭВМ и систем : Учебник для вузов / Б.Я. Цилькер, С.А. Орлов. - 2-е изд. - СПб.: Питер, 2011. - 688 с.

8. Шаляпин В. В. Основы микропроцессорной техники: учеб пособие / / 2011. — 207 с.

9. Department of Computer Science Southern Illinois University, Carbondale CS 401 COMPUTER ARCHITECTURE; RISC versus CISC Architecture http://www2.cs.siu.edu/~cs401/Textbook/ch4.pdf

10. Designing Embedded Hardware, 2nd Edition - Create New Computers and Devices by John Catsoulis. - O'Reilly Media 400 pages, 2009

11. Introduction to the MIPS Architecture by Robert Britton, 2013

12. M68000 Microprocessor Users Manual (9th Edition); Motorola (Freescale); 224 pages; 1996.

- Анализ и оценка средств реализации объектно-ориентированных методов анализа и проектирования экономической информационной системы.

- Сетевая форма организации бизнеса.

- Эффективность менеджмента организации (Понятие и сущность эффективности менеджмента предприятия)

- Налоги и налогообложение

- Организационная культура и ее роль в современных организациях

- Нотариат и его р оль в защите гражданских прав и охраняемых законом интересов

- Ценовые войны в теории и на практике.

- Методы кодирования данных (Общие принципы кодирования данных)

- Анализ и оценка средств реализации структурных методов анализа и проектирования экономической информационной системы..

- Рынок ценных бумаг

- Применение процессного подхода для оптимизации бизнес-процессов

- Варианты архитектуры «клиент - сервер».