Процессор персонального компьютера. Назначение, функции, классификация процессора

Содержание:

ВВЕДЕНИЕ

Сегодня современный мир без использования персонального компьютера – практически немыслимое явление.

Стоит отметить, что мало кто задумывался, как именно построены такие элементы вычислительной техники. Также, намного меньше людей знают, насколько развитыми стали указанные аппараты на протяжении всего последних 30-40 лет.

Для самых разных категорий пользователей искусственный интеллект, персональный компьютер (ПК) являются аналогичными вещами.

Сегодня любой прорыв для компьютерных информационных технологий может встречаться очень громкими лозунгами, как процесс, что выделятся среди других особо. Люди хотят, чтобы у них был младший брат, что может соображать быстрее своих владельцев.

Процессор – главный «мозговой» узел, что выполняет программный код непосредственно в памяти ПК.

В теперешнее время в случае упоминании понятия «процессор» часто подразумевают микропроцессор – специальная электронная схема, которая может содержать непосредственно кроме процессора также и иные узлы – к примеру, кэш-память.

Актуальность для выбранной тематики повязана также и с тем, что все теперешние компьютеры не могут обходится без использования своего «мозга» – процессора, и чем он мощнее, тем и ПК является более производительным.

То есть, при подборе ПК для покупки необходимо также разбираться и в характеристиках оборудования процессора ПК и его составных частей.

Объектом курсовой работы являются принципы построения современных ЭВМ.

Предмет работы – принципы построения процессора ПК.

Цель курсовой работы является описанием главных принципов построения центрального процессора, его структуры и системы команд.

В соответствии с целью курсовой работы поставлены такие задачи:

– провести подробный анализ источников литературы по аппаратной части ЭВМ;

– дать характеристику главным принципам фон Неймана;

– выполнить ознакомление с системой команд процессора ЭВМ;

– рассмотреть структуру оборудования процессора;

– проанализировать принципы функционирования процессора.

Проблемы, что связаны с аппаратной частью всех персональных компьютеров исследовали ученые, как П.Виннер, Р.К. Малькович, В.С. Королюк.

1.ТЕОРЕТИЧЕСКИЕ ОСНОВЫ ФУНКЦИОНИРОВАНИЯ ЭВМ

1.1. Принципы Джона фон Неймана

Абсолютное большинство теперешних процессоров ЭВМ в общем основываются на различных версиях циклического процесса по обработке разной последовательной информации, изобретённых еще Дж. фон Нейманом в 1946 г. Данный ученый придумал полностью рабочие схемы для постройки ЭВМ.

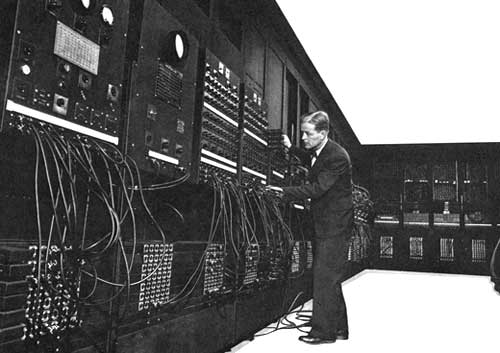

В результате американец начал создавать ЭВМ для выполнения мониторинга береговой ПВО США, которая была реализована при использовании машины "ENIAС" (аббревиатура от «электронный численный интегратор и автоматический вычислитель») (рисунок 1).

Заметим тот факт, что проектируемая машина также была использована с огромным недостатком: в ней устройства вовсе не были для запоминания команд, которые были предназначены процессору.

Рисунок 1 – ЭВМ «ЭНИАК»

В 1944 году ученый выступил на конференции, где и рассказал о своей работе, в котором были использованы основные принципы организации вычислительных устройств, которые имели название "архитектура Джона фон Неймана".

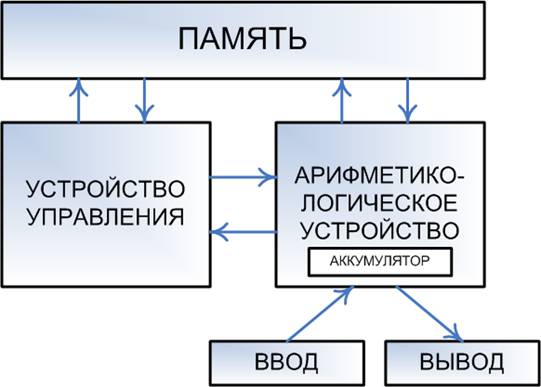

Типовая схема архитектуры показана на рисунке 2.

Рисунок 2 – Основные компоненты ЭВМ в схеме фон Неймана

В рассмотренный состав обычной ЭВМ должны входить перечисленные составные компоненты:[5]

– арифметико-логическое устройство;

– модули памяти;

– внешние устройства разделяются: [10]

1) устройства для внешней памяти;

2) устройства для вывода и для ввода информации;

– разные управляющие устройства.

Рассмотрим все основные принципы для созданной архитектуры ученого фон Неймана:[15]

- Принцип однородности используемой памяти компьютера – все команды, что имеются и используются при обработке данные могут быть сохранены в ячейках памяти.

- Принципы адресности [20] подразумевает то, что основная память использует множество ячеек.

- Принципы программного управления подразумевают то, что практически любые вычисления, которые каким-то образом могут использоваться алгоритмом в решении разного рода задач, как-то должны представляться и в программе, что состоит из некоторой последовательности выполняемых команд. Каждая из таких команд предписывает последовательность по всей совокупности операций, что далее реализуются в ЭВМ. [4]

- Принцип использования бинарного кодирования – согласно которому, полностью все данные, а также и команды для работы с ними, кодируются при использовании бинарных цифр. Все форматы данных представляются посредством некоторой двоичной последовательности.

Опишем алгоритм функционирования любого устройства для управления данными, которое являлось предком для процессора.

В самых различных переходных архитектурах, а также с выполнением различных программных команд могут потребоваться и дополнительные этапы обработки информации.

Например, для реализации арифметических операций могут быть скорее всего востребованы дополнительные запросы по ячейках оперативной памяти ЭВМ, во время них будет производится считывание различных операндов, а записи результатов.

Также одной с самых отличительных особенностей для классической архитектуры фон Неймана являлось хранение инструкций и кода для написания операций с имеющимися данными.

Далее рассмотрим циклы по выполнению:[8]

- Процессор выставляет некоторое специальное число, хранящееся также в его регистре, потом отдаёт памяти команды прочтения;

- Выставленное число будет являться при этом для используемой памяти ее непосредственными адресами; а память, получив указанный конкретный адрес и операции для чтения, будет при этом выставлять содержимое, хранящееся по адресу;

- Процессор получает заданное число, направленное с шины данных, потом его преобразовывает как обычную команду (инструкцию) с системой команд, и реализует её;

- В случае неразличения последней команды, а именно команды перехода, процессоры увеличивают на единицу (при предположении, что такая длина для команд равна будет единице) числа, которые будут храниться в счётчике; то при этом в результате образуются адреса для выполнения всех последующих команд;[12]

- Снова выполняется этап №1.

Рассмотренный цикл выполняется неизменно всегда, и именно он и называется процессом.

1.2. Обзор архитектуры классического ПК

Рассмотрим архитектуру ЭВМ, а именно предназначение основных ее узлов и оборудования.

Рисунок 4 – Процессор

Центральный процессор – это микропроцессор со всеми микросхемами, вспомогательными компонентами, включая и внешнюю специальную кэш-память, контроллеры для системной шины и др.(рисунок 3).

В большинстве всех случаев именно такое устройство будет осуществлять процесс обмена для системной шины.[12]

Оперативная память может занимать динамическое пространство памяти непосредственно для процессора. Но также ее объем бывает чаще всего меньше (рисунок 4).

Рисунок 4 – Оперативная память

В современных ЭВМ объем системной оперативной памяти составляет до 16 Гб. Оперативная память выполняется также на разных микросхемах и поэтому нужно ее регенерировать со временем.

Постоянная память имеет возможность использовать небольшой объем, содержать программу для начального запуска ЭВМ, описания конфигурации системы, а также другие драйверы и дополнительные программы (подпрограммы для нижнего системного уровня) при выполнении взаимодействий между системными устройствами.

Контроллер для прерываний может выполнять преобразование всех аппаратных методов и прерываний системной платы в самые разные аппаратные прерывания для процессоров, а также задают адреса для направления процесса прерывания.

Все данные режимы контроллера прерываний могут задаваться непосредственно процессором.

Контроллер для прямого доступа (рисунок 5) предназначен для принятия запросов на ПДП прямо из системной магистрали, передавать сигнал процессорам, предоставления процессором магистралей выполняет пересылку данных между блоками памяти.

Рисунок 5 – Контроллер для реализации прямого доступа

Системные устройства для ввода/вывода – устройства, которые также нужны для работы конкретного ПК, взаимодействия с стандартными такими устройствами по интерфейсам (последовательному, параллельному). Они также могут реализовываться на любой материнской схеме, а также и на платах с расширениями.[16]

Платы расширения могут устанавливаться в специальные слоты на системной магистрали, содержать разные, устройства для ввода/вывода и оперативную встроенную память.

В рассмотренном традиционном случае обмен между ячейками памяти выполняется только с максимально возможной скоростью для определенного типа процессора.

Заметим, актуальным в нынешнее время становится быстродействие непосредственно центрального процессора[3].

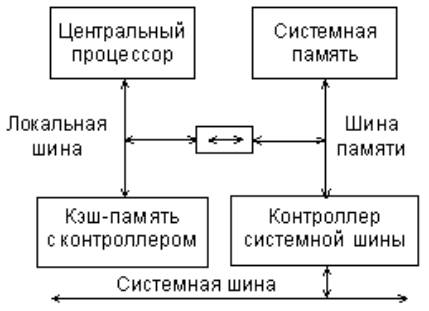

Таким образом, структура традиционной ЭВМ из одношинной, что используема только в самых первых ПК, является мультишинной (рисунок 6).[6]

|

|

||

|

Рисунок 6 – Организация связи в мультишинной структуре |

Рассмотрим далее предназначение шин:

– к обычной шине локального масштаба могут быть подключены процессор, кэш-память;

– к шинам для памяти можно подключать постоянную и оперативную память для ПК;

– к системной шине подключаются часто все иные устройства.

Рисунок 7 – Принцип работы ЭВМ

Все 3 шины ЭВМ располагают разными адресными потоками, линиями данных, что управляют сигналами. Но состав и назначение линий для указанных шин не совпадают также между собой, но они могут при этом выполнять очень похожие функции.

В первом разделе курсовой работы рассмотрены некоторые основные определения об использовании аппаратной части ЭВМ, описаны 4 принципы Джона фон Неймана, охарактеризованы все основные узлы архитектуры ЭВМ.

2. УСТРОЙСТВО И СХЕМА КЛАССИЧЕСКОГО ПРОЦЕССОРА

2.1. Принцип построения процессора

Центральный процессор ЭВМ является исполнителем машинных программных инструкций, составная часть аппаратного обеспечения ЭВМ или логического контроллера, используемого при написания блоков программного кода, отвечающая при выполнении самых различных арифметических и программных операций, которые могут задаваться программами из операционных систем, а также и координирующий любую работу всех устройств ЭВМ.[9]

Центральный процессор является мозгом компьютера, а его главное задание – выполнять программные продукты, находящиеся непосредственно в памяти ЭВМ.

Процессоры вызывают команды непосредственно с памяти ПК, может определять их тип, также их выполнять одну за другой. Компоненты соединены специальной шиной, что представляется набором некоторых связанных проводов, а по ним передаются адреса, сигналы и данные для управления.

Все шины разделены на внешние (связывающие процессор с памятью, а также устройствами по вводу-выводу) и внутренние.

Современным процессором является сложное и высокотехнологическое устройство, которое может в себя включать самые последние достижения для области вычислительной техники.[5]

Большинство процессоров состоит с:

- контроллера ОЗУ;

- ядер, которые осуществляют выполнение разных программных инструкций;

- контроллера для использования работы системной шины (HT, QPI и т.п.);

Все процессоры характеризуются следующими основными параметрами:

- типом микроархитектуры оборудования;

- тактовой частотой;

- совокупностью команд;

- количеством уровней для памяти;

- скоростью и типологией системной шины;

- отсутствием контроллера;

- объемом используемой памяти;

- типом и функционалом поддерживаемой ОЗУ.

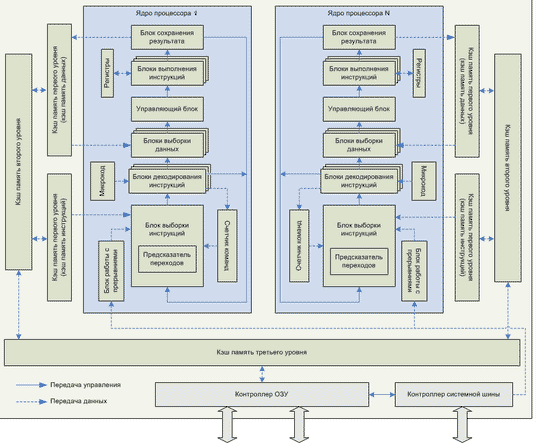

Упрощенная схема центрального процессора показана ниже на рисунке 8.

Рисунок 8 – Построение центрального микропроцессора

2.2. Структура процессора

Ядро процессора является основной частью, которая может содержать практически все функциональные блоки и осуществляет выполнение всех логических, арифметических операций с данными.

На рисунке 8 указана также и структурная схема для ядра процессора. Как видно, практически все ядра для центрального процессора могут состоят с блоков:

- выборки;

- данных;

- управления;

- декодирования;

- сохранения результатов;

- набора регистров;

- выполнения инструкций;

- прерываний;

- микрокода;

- счетчики разных команд.

Блок выборки также может осуществлять считывание программных команд по их установленному адресу, указанному на счетчике каждой команды. За каждый такт может считываться сразу несколько программных инструкций.

Количество всех обрабатываемых инструкций обусловлено также и общим количеством блоков при декодировании, поскольку необходимо также загрузить в каждом такте максимально процесс декодирования.

При оптимальной работе декодирования, а также в ядре для процессора есть специальный распределитель переходов, который и выполняет определение, какая последовательность программных команд будет выполняться после выполнения переходов.

Этот факт также очень необходим, для того, чтобы после выполненного перехода максимально нагрузить ядро.

Блоки декодирования являются специальными блоками, что занимаются процессом для декодирования инструкций, они определяют, что нужно сделать определенному процессору, какие такие вспомогательные данные надобны для корректной реализации инструкции.

Задача для блоков в большинстве современных процессоров, построенных на базе концепции CISC, считаются очень сложными. Дело также в том факте, что длина инструкций, а также количество разных операндов бывает разное, нефиксированное, а это сильно может усложнять всю работу разработчиков процессоров, а также и делает процесс декодирования совсем нетривиальным.

Часто такие отдельные команды могут заменять специальным микрокодом, то есть серией простых команд, что в своей совокупности выполняют аналогичные действие, что и только одна сложная инструкция. микрокод записан в область с ПЗУ. [18]

К тому же микрокод упрощает саму разработку процессоров, ведь при этом отпадает необходимость при реализации сложноустроенных структур для ядер выполнения его отдельных инструкций, а также выполнить исправление такого микрокода намного проще.

Во многих современных процессорах, обычно, могут рассматривать сразу несколько блоков по декодирования использованных программных инструкций.

Для процессоров класса Intel Core 2 ядра могут содержать по 2 таких компонента.

Блоки для выполнения выборок данных осуществляют свой отбор данных из специальной кеш-памяти или ОЗУ, что необходимы для корректной реализации текущих инструкций.

Практически все процессорные ядра могут содержать несколько блоков с реализованной выборкой данных. Например, в таких процессорах как Intel Core будут использоваться только 2 блока с выборкой на каждое физическое ядро.

Управляющий блок на базисе декодированных инструкций управляет непосредственным функционированием блоков для реализации инструкций, также распределяет практически всю нагрузку для них, а при этом обеспечивает и своевременное, верное выполнение абсолютно всех инструкций.

Все это является одним из важнейших элементов ядра процессора.

Блоки выполнения инструкций могут в себя включать несколько самых разных компонентов:[2]

- ALU – арифметическое логическое устройство;

- FPU – устройство операций.

Блоки для выполнения процесса обработки расширений реализуются с помощью наборов разных инструкций.

Дополнительные операции могут использоваться для реализации работы с несколькими более быстрыми потоками данных, дешифрования, кодирования видео.

Для такой работы на каждое ядро процессоров могут вводить регистры, а также специальные совокупности логики. Популярными расширениями таких совокупностей инструкций являются следующие:[14]

– MMX – набор, что может быть разработан организацией Intel, для обработки аудио- и видеоинформации;

– SSE – набор инструкций, что разработанный компанией Intel, с помощью описания последовательности операций над некоторым множеством информации при его распараллеливании некоторым вычислительным процессом.

Все такие наборы команд усовершенствуются практически постоянно, и на определенный момент имеются самые разные ревизии [7].

– ATA – это набор программных инструкций, который был еще разработан компанией Intel, для реализации выполнения ускорения функционирования только специализированного ПО, снижения процесса энергопотребления в использовании программных продуктов. Эти инструкции используются при вычислении разных контрольных сумм, поиска требуемых данных;

– 3DNow – набор из программных инструкций, который был разработан фирмой AMD, как расширении MMX;

– AES – это набор программных инструкций, что разработан для программ Intel, для ускорения всех выполняемых приложений, использующих конфиденциальный тип шифрования данных.

Блок для реализации сохранения результатов дает все возможности записать результат при выполнению по инструкции в памяти при использовании адресов, указанных в инструкции.[1]

Блок работы с системными прерываниями – выполняет самую важнейших задач для центрального процессора, которая позволяет полностью. своевременно реагировать на разные события, реализовать прерывания хода работы выполнения программы, осуществлять все требуемые команды от него.

Также благодаря наличию прерываний, процессоры способны к выполнению параллельной многозадачности.

Обработка таких прерываний может в большинстве случаев выполняется указанным далее образом.

Процессоры для осуществления каждого из циклов в работе могут проверять самые наличие специального запроса.

Если наблюдается прерывание обработки, процессор должен сохранять адрес для инструкции в определенный стек, который ему необходимо выполнять, и данные, получены после выполнения самой последней инструкции, процессор переходит далее к реализации функций по обработке разного прерывания.[1]

После окончания реализации указанных функции обработки прерываний, с созданного стека будут считываться непосредственно сохраненные данные в него, а устройство микропроцессора возобновляет выполнение ранее уже поставленной задачи.[7]

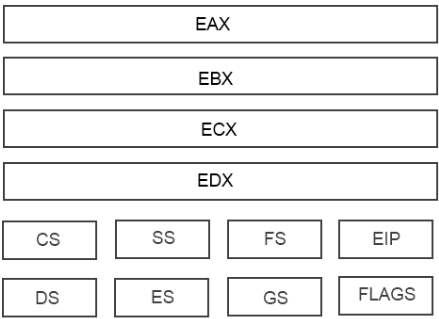

Регистры процессора – это сверхбыстрая память очень небольшого объема, что входит непосредственно в их состав центрального микропроцессора, а при хранении некоторых промежуточных результатов с уже выполненных инструкциях (рисунок 9).

Практически все регистры процессора можно описать с помощью таких 2-х типов:

– регистры с общим назначением;

– специальные проблемно-ориентированные регистры.

Рисунок 9 – Классы регистров

Регистры для общего использования применяются при реализации разного рода арифметических, логических операций, выполнение специфических операций для самых разных дополнительных наборов и инструкций.

Регистры для такого специального назначения могут содержать также системные данные, что часто необходимы для работы указанного конкретного процессора.

Счетчик команд – является регистр, содержащий адрес всех команд, которые процессор начнет реализовать после следующего такта в работе (рисунок 10).[1]

Рисунок 10 – Регистр считчика команд

Во втором разделе рассматривались все основные понятия об устройстве центрального процессора, описаны все составные его части, структура, а также и некоторые характеристики.

3.СИСТЕМА КОМАНД ПРОЦЕССОРА

3.1.Поняние системы команд процессора

Система команд – набор допустимых для определенного процессора управляющих кодов, способов адресации данных. Системы команд жестко связаны с конкретным видом процессора, поскольку также определяется аппаратной структурой для блока дешифрации разных команд, и не обладает обычно переносимостью на иные типы процессоров (хотя часто имеет место совместимость типа “снизу-вверх” в рамках целой серии процессоров).[11]

Типовая структура для формата команды:

– КОП – код операци1 – это двоичный код, что однозначно указывает процессору на выполнение разных конкретных действий (пересылка, сложения и т.д.), и определяющий форму задания при этом адресов операндов;

– АЧ – адресная часть – это двоичное число, что может представлять собой адреса операндов, значение операндов, адрес следующей операции (адрес перехода).[13]

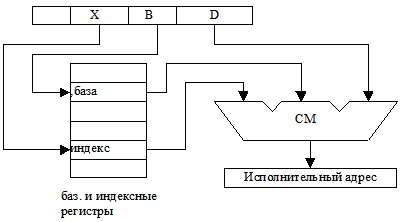

При обработке огромных массивов данных, выбираемых друг за другом последовательно, нет никакого смысла постоянно обращаться к памяти за новыми адресами.

Для этого также достаточно автоматически менять все содержимое для специального регистра, что называется индексным, чтобы выбрать последовательно размещенные данные.

Такой индексный регистр является также косвенным. Его загружают с начальным адресом массива (командой). Дальнейшая адресация может осуществляться путем автоматического добавления и вычитания единицы или этапа адреса с его содержимого (рисунок 11).

Рисунок 11 – Формирование адреса операндов при индексной адресации

В общем случае системы команд процессора включают в себя следующие 4 основные группы:[17]

– арифметические команды;

Команды для пересылки данных вовсе не требуют выполнения операций над операндами. Такие операнды просто пересылаются (копируются) из источника в приемник.

Источником и приемником часто могут быть разные внутренние регистры процессоров, ячейки памяти или же устройства ввода/вывода

В соответствии из результатами каждой выполненной команды будут устанавливаться или очищаться биты регистра состояния центрального процессора (PSW).

Но стоит помнить, что далеко не все команды могут изменять все имеющиеся флаги в PSW. Это также определяется особенностями для каждого конкретного процессора.

Для разных процессоров системы их команд существенно различаются, а в основе они очень похожи. Число команд у процессоров очень различно. Например, в процессоре МС68000 61 команда, а у классического процессора 8086 – аж 134 команды.

Для современных мощных процессоров число команд достигает и нескольких сотен. В это же время существуют разные процессоры с сокращенным перечнем команд (RISC-процессоры), в которых также за счет максимального сокращения числа команд достигается увеличение уровня эффективности и скорости выполнения.

3.2. Обзор категорий системы команд

Команды для пересылки данных занимают важное место в системе любого процессора. Они реализуют следующие важнейшие функции:

– загрузка содержимого в регистры процессора;

– сохранение содержимого в памяти внутренних регистров;

– копирование содержимого с одной области в другую;

– запись с помощью устройств ввода/вывода и чтения.

В некоторых процессорах все эти функции могут выполняться одной единственной операцией MOV но с разными методами адресации их операндов.

В иных процессорах помимо операции MOV имеется несколько команд для реализации перечисленных функций. К примеру, для загрузки регистров используются команды загрузки, причем также для разных регистров применяются разные команды (обозначения их обычно строятся с применением слова LOAD).

Часто выделяются и специальные команды для выполнения сохранения в стеке или для извлечения с стека (POP – извлечь со стека, PUSH – сохранить).

Такие команды выполняют пересылку от автоинкрементной и автодекрементной адресации.[19]

Иногда в системы команд вводятся специальные команды MOVS для строчной пересылки данных. Эта команда пересылает вовсе не одно слово (байт), а заданное количество байтов или слов (MOVSB), то есть инициирует даже не один цикл для обмена по магистралям, а несколько. В таком случае адрес памяти, с которым и происходит взаимодействие, увеличивается сразу на 1 или 2 после каждого их обращения или уменьшается на 1 или 2 после каждого такого обращения. То есть применяется в неявном виде автоинкрементная и автодекрементная адресация.

В процессорах специально выделяются функции для обмена с устройствами, которые отвечают за ввод/вывод.

Команда IN используется при вводе (чтении) информации с устройства ввода/вывода, а команды OUT используются для вывода в устройство по вводу/выводу.

Обмен информацией для этого производится между регистром-аккумулятором, а также устройством ввода/вывода.

Также к командам пересылки данных относятся команды обмена данными (их обозначения строятся на основании слова Exchange ). Также может быть предусмотрен и обмен информацией между разными внутренними регистрами, между 2-я половинами одного регистра (команда SWAР) или между регистром с ячейкой памяти.

Арифметические команды используют коды операндов как имеющиеся числовые двоичные и двоично-десятичные коды. Такие команды могут быть распределены на 5 основных групп:

– команды с фиксированной запятой;

– команды декремента и инкремента;

– команды операций с плавающей точкой;

– команды очистки;

– команда сравнения.

Команды для операций с фиксированной точкой работают и с кодами в регистрах процессоров или в памяти с обычными бинарными кодами.

Команда сложения (ADD) возвращает сумму 2-х кодов.

Команда вычитания (SUB) возвращает разность 2-х кодов.

Команда для умножения (MUL) вычисляет произведение 2-х кодов (разрядность результата является вдвое больше разрядности его сомножителей).

Команда для деления (DIV) вычисляет частное с деления одного на другой кода. Причем все такие команды могут работать и с числами с знаком, и с числами без него.

Команды операций для плавающей точки используют формат представления значений с порядком, а также мантиссой (обычно такие числа занимают 2 последовательные ячейки памяти).

В нынешних мощных процессорах набор таких команд с плавающей запятой вовсе не ограничивается лишь четырьмя арифметическими действиями, содержит и множество иных более сложных команд, к примеру, вычисление тригонометрических, логарифмических функций, сложных функций, что необходимы при обработке изображения и звука.

Команды очистки предназначены для обработки нулевого кода в регистры или ячейки памяти. Эти команды также могут быть заменены операциями пересылки нулевого кода, хотя специальные команды очистки выполняются обычно быстрее, чем команды для пересылки.

Команды для очистки иногда относятся к группе логических операций, но суть их не меняется от этого.

Команды инкремента и декремента также бывают удобны. Их можно заменить в принципе командами суммирования на единицу или вычитания единицы, хотя инкремент и декремент будут выполняться быстрее, чем суммирование или вычитание.

Такие команды требуют только одного входного операнда, что одновременно является выходным операндом.

Команда сравнения (CMP) предназначена для сравнения 2-х входных операндов. Она по сути вычисляет разность для этих двух операндов, но какого-то выходного операнда она не формирует, а лишь изменяет биты для регистра состояния процессора по результату такого вычитания.

Следующая команда за командой сравнения будет анализировать биты для регистра состояния процессора, а также выполнять действия от их значений.

В некоторых процессорах также предусмотрены команды для цепочечного сравнения 2-х последовательностей операндов, что находятся в памяти.

Логические команды выполняют логические (побитовые) операции над операндами, то есть они выполняют рассмотрение кодов операндов не как число, а как совокупность отдельных битов.

Логические команды выполняют операции:

– сложение по модулю 2, логическое И, ИЛИ;

– логические, арифметические или циклические сдвиги;

– проверка операндов и битов;

– установка и очистка совокупности битов регистра состояния процессора.

Команды для логических операций позволяют вычислять побитно основные логические функции с двух входных операндов.

Также операция И (AND) применяется для принудительной очистке заданных битов.

Операция ИЛИ (OR) применяется при принудительной установки заданных битов.

Операция "Исключающее ИЛИ" (XOR) применяется для инверсии заданной совокупности битов

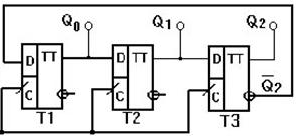

Команды сдвигов (рисунок 12) позволяют побитно сдвигать программный код операнда вправо. Тип сдвига (арифметический, циклический или логический) определяет, каково будет значение старшего бита или младшего бита, а также определяет, есть ли где-то сохранено значение прежнее старшего бита или младшего бита.

Рисунок 12 – Реализация сдвигов

Команды переходов предназначены при организации всевозможных циклов, вызовов подпрограмм, ветвлений и т.п., то есть они также нарушают последовательный ход реализации программы.

Такие команды записывают в регистре-счетчик команд некоторое новое значение и вызывают тем самым переход процессора не к следующей команде по порядку, а также к любой другой команде для памяти программ. Некоторые такие команды переходов предусматривают возврат назад в дальнейшем, в точку, с которой был сделан прежний переход, другие же не предусматривают этого.

Когда возврат предусмотрен, то параметры процессора сохраняются непосредственно в стеке.

Команды переходов делятся на две группы:

В обозначениях таких команд используются термины Branch ( ветвление ) или Jump (прыжок).

Команды для безусловных переходов вызывают также переход в новый диапазон памяти независимо ни от чего. Также они могут вызывать переход в указанную величину смещения или же на конкретно указанный адрес памяти.

Команды условных переходов используются в переходах не всегда, а лишь при выполнении некоторых заданных условий. В качестве этих условий обычно выступают и значения флагов в регистрах состояния процессора.

В результате написания последнего раздела курсовой работы подробно рассмотрены операции для реализации систем команд, описаны главные их категории, приведены примеры самых востребованных из них.

ЗАКЛЮЧЕНИЕ

Все процессоры предназначены для выполнения в определённой последовательности некоторых операций и исполнять их. Все инструкции процессора предназначаются часто для пересылки, быстрой обработки, качественного анализа имеющихся данных, расположенных непосредственно в памяти ЭВМ и портах по вводу/выводу данных, а также в организации структур по реализации ветвления и переходов в различные вычислительные процессы.

В многопроцессорной системе ЭВМ самые основные функции, что выполняются центральным процессором могут являться распределенными также между несколькими идентичными сопроцессорами с целью увеличения их производительности.

В помощь процессорам для ЭВМ также вводят и специальные устройства – сопроцессоры, которые ориентированы в эффективное применение специфических функций ЭВМ.

Также широко распространенными считаются математические сопроцессоры, которые также будут эффективно обрабатывать разные числовые данные с форматами данных с плавающей точкой, графические сопроцессоры для легкого воспроизведения видео- и мультимедийной информации, которые выполняют разного рода геометрические построения, обработку всех изображений, также сопроцессоры с вводом/выводом данных, которые разгружают сам процессор от операций по взаимодействию его с различными периферийными устройствами.

В работе выполнены такие следующие задачи:

– проведен подробный анализ источников литературы по аппаратной части ЭВМ;

– дана характеристика главным принципам фон Неймана;

– выполнено ознакомление с системой команд процессора ЭВМ;

– рассмотрена структура оборудования процессора;

– проанализированы принципы функционирования процессора.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

- Аногилев Н.И. Информатика, Учебник для ВУЗов – М.: Издательство Academa, 2015. - 268 с.

- Бойс Д. Осваиваем ПК. Русская версия. М.: Издательство Academa, 2015.-320 с.

- Денисов А. Аппаратное обеспечение ПК. – Спб: Питер, 2015. - 461 с.

- Евдокимов В.В. и др. Состав ПК. Учебник для вузов. Под ред. д. э. н., проф. В.В. Евдокимова. СПб.: Питер паблишинг, 2016.-382 с.

- Информатика. Базовый курс. Учебник для Вузов/под ред. С.В. Симоновича, - СПб.: Питер, 2013.-142 с.

- Информатика: Учебник/под ред. Н.В. Макаровой. - М.: Финансы и статистика, 2014. - 768 с.

- Корбюзье Архитектура ПК: моногр. / Корбюзье, Ле. - М.: Прогресс, 2014. - 304 c.

- Кушнир, И.И. Архитектура ПК / И.И. Кушнир. - М.: Лениздат, 2015. - 144 c.

- Лин, В. PDP-11 и VAX-11. Архитектура ЭВМ и программирование на языке ассемблера / В. Лин. - М.: Радио и связь, 2013. - 320 c.

- Максимов, Н. В. Архитектура ЭВМ / Н.В. Максимов, И.И. Попов, Т.Л. Партыка. - М.: Форум, 2015. - 512 c.

- Максимов, Н. В. Архитектура вычислительных систем / Н.В. Максимов, И.И. Попов, Т.Л. Партыка. - М.: Форум, 2016. - 204 c.

- Максимов, Н. В. Архитектура и схемотехника / Н.В. Максимов, И.И. Попов, Т.Л. Партыка. - М.: Форум, Инфра-М, 2017. - 612 c.

- Манизер, Г. Архитектура ЭВМ / Г. Манизер, П. Тельтевский. - М.: М: Советский художник, 2014. - 687 c.

- Новожилов, О. П. Архитектура ЭВМ и систем / О.П. Новожилов. - М.: Юрайт, 2013. - 528 c.

- Основы современных компьютерных технологий. Ред. Хомченко А.Д. Симонович С. В., Евсеев Г.А., Практическая информатика, Учебное пособие. М.: АСТпресс, 2014.-400 с.

- Симонович С.В. Специальная информатика, Учебное пособие. М.: АСТпресс, 2015.-310 с.

- Схемотехника/ Под ред. Н.В. Макаровой. - М.: Финансы и статистика, 2013.-200 с.

- Фигурнов В. Э. IBM PC для пользователя. М.: Инфра-М, 2013.-410 с.

- Шкаев А.В. Руководство по работе на персональном компьютере. Справочник. М.: Радио и связь, 2014.-210 с.

- Шпарин В.А. Устройство ЭВМ. М.: Наука, 2015.-356 с.

- Анализ и оценка средств реализации структурных методов анализа и проектирования экономической информационной системы

- Курсовая работа

- Налоговой контроль и налоговые проверки

- Особенности употребления пословиц в современном английском языке

- Ложные друзья переводчика

- Основные этапы формирования налогового учета в России

- Содержание и специфические особенности предпринимательской деятельности в сфере строительства

- Современные языки программирования

- Проектирование реализации операций бизнес-процесса «Реализация билетов через розничные кассы»

- Современные языки программирования»

- Виды и состав угроз информационной безопасности

- Способы представления данных в информационных системах